Intel do „Ivy Bridge“ (22nm proces) použije „3D tranzistory“

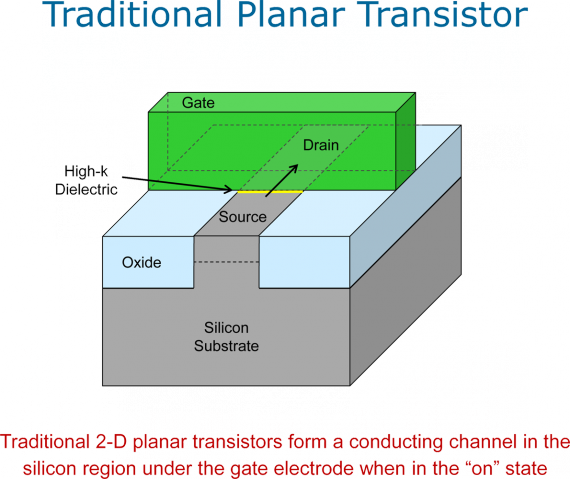

Intel sice o těchto tranzistorech hovoří jako o „3-D“, ale to neznamená, že by současné tranzistory byly dvojrozměrné (to by se musely dělat na grafenu ;-), a to i přes skutečnost, že je Intel v podstatě „dvojrozměrnými“ nazývá, přesněji řečeno „plochými“ (planar). Jde o to, že doposud se ta část tranzistorů, kudy teče elektrický proud („vodící kanál“), dělala v rovině křemíkové desky a na ni se pak aplikovaly další vrstvy, z nich se v průběhu výrobního procesu staly „gate“ (řídící elektrody) tranzistorů. Zjednodušeně řečeno tok elektronů byl realizován v podstatě „dvourozměrně“ (na povrchu této vodící vrstvy).

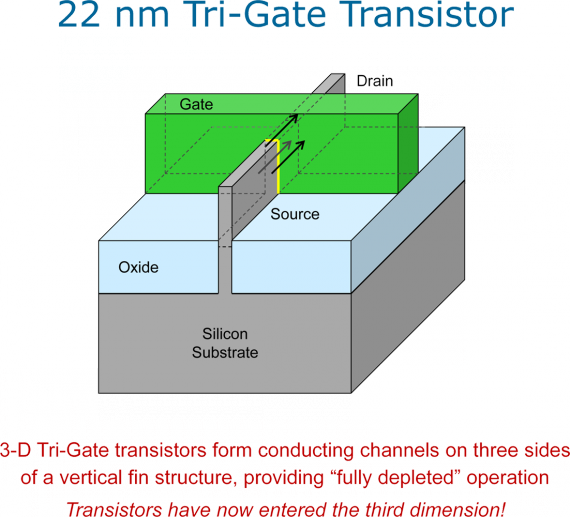

To, co nyní Intel zavádí, vzdáleně připomíná kolmý záznam na plotnách pevných disků. Tam se také před příchodem této technologie magnety „válely“ na plotnách, aplikací kolmého záznamu se „postavily“ a vešlo se jich vedle sebe více. Primárním cílem Intelu v „postavení“ vodícího kanálu v tranzistoru však není potřeba nacpat jich více vedle sebe, ale zvýšení výkonu a snížení spotřeby energie. Ostatně při výrobě tranzistorů v procesorech se výrobci snaží o dvě základní věci: aby byly tranzistory co nejrychlejší (tedy mít schopnost co nejrychleji se spínat) a aby propouštěly co nejméně energie v případě „zavření“ hradla. „Tri-gate“ tranzistory umožňují zlepšit obojí.

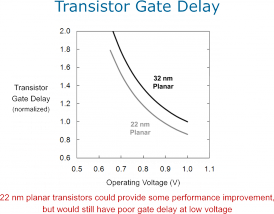

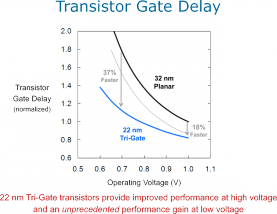

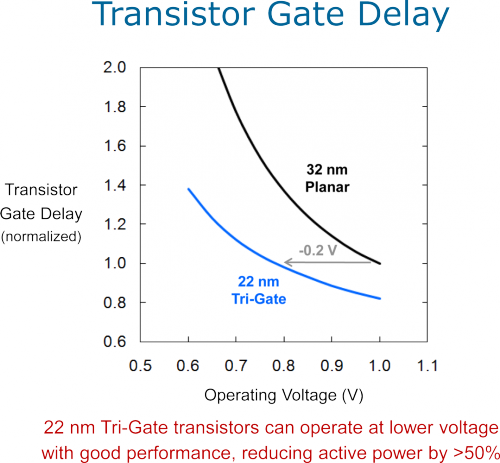

Obrázek vlevo ukazuje, k jakému zlepšení by v tomto ohledu došlo pouhým přechodem z 32nm na 22nm proces bez aplikace „tri-gate“ tranzistorů. Obrázek vpravo k tomu právě přidává vliv „tri-gate“ tranzistorů. Technologie umožňuje u standardně napájených procesorů zvýšit rychlost o 18 % a u energeticky nenáročných procesorů dokonce až o 37 %. Ještě se můžeme podívat na třetí graf, který říká, že při zachování výkonu je možné snížit napájecí napětí o 0,2 V, což ale v celkovém čipu sníží spotřebu energie na polovinu.

Jinými slovy: kdyby Intel nyní začal vyrábět touto technologií stejně rychlé procesory jako dnes, mohl by jim dát poloviční hodnotu TDP. Je však nadmíru jasné, že „Ivy Bridge“ procesory budou především rychlejší. Implementace „tri-gate“ tranzistorů zdražuje výrobu pouze o 2 až 3 %.

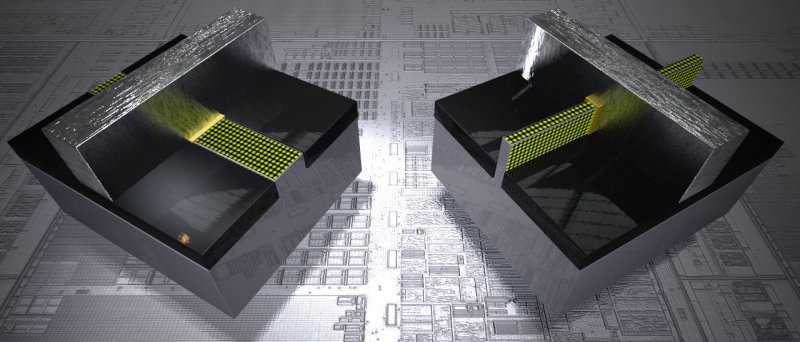

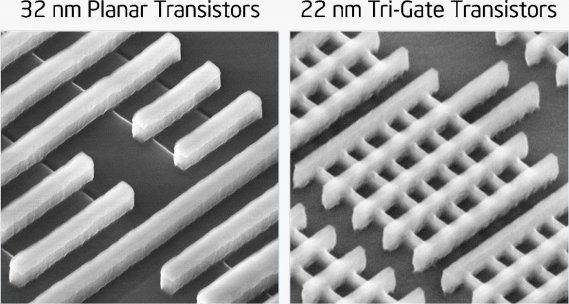

Finta této metody spočívá navíc ještě v jedné věci, zde se v přirovnání opět vrátíme ke kolmému záznamu na plotnách pevných disků, kdy se „postavením“ magnetů dalo docílit zvýšení jejich počtu na plošnou jednotku. Stejné je to i s „vodícími kanály“ tranzistorů, které se po postavení „fins“ (v podstatě „žebra“, protože ono je to připomíná) vyskytují na všech třech stranách těchto „žeber“ (vlevo, vpravo i nahoře). S postavením těchto „žeber“ je možné jich dát pod jedno hradlo vedle sebe více. Tím se dá vytvořit „silnější“ tranzistor schopný vyššího výkonu. Na obrázcích představujících zvětšeniny těchto tranzistorů je těchto „žeber“ na jeden tranzistor třeba šest.

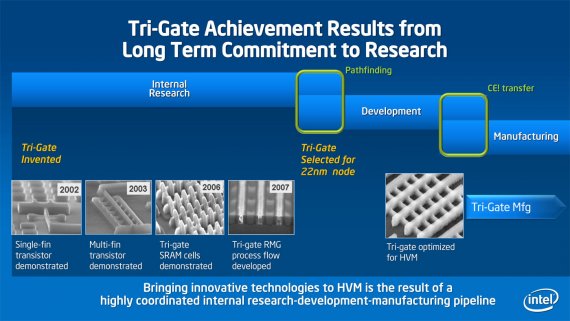

Jak již bylo řečeno, Intel se začal vývojem „tri-gate“ tranzistorů zabývat zhruba před dekádou. Už v roce 2002 demonstroval první „trojrozměrný“ tranzistor s jedním takovým žebrem. O rok později zvládl více „žeber“ a v roce 2006 vytvořil první vzorek SRAM čipu s „tri-gate“ tranzistory. Nyní má již hotovy funkční vzorky procesorů „Ivy Bridge“ na 22nm procesu s „tri-gate“ tranzistory a proces je již optimalizován pro velkovýrobu.

Stručně vám přechod z „plošného“ na „3D“ tranzistor vysvětlí na videu Mark Bohr. Na webu Intelu pak můžete zhlédnout celou téměř hodinovou tiskovou konferenci, kde Intel tento průlom ve výrobě čipů představil.

A co bude dál? O tom Intel hovořil už v roce 2006, nástupcem „tri-gate“ tranzistorů by mohly být namísto „žeber“ nanotrubičky procházející přímo řídící elektrodou (gate). O tom si ale budeme povídat odhadem nejdříve za dva roky.