Intel představil Tiger Lake-U: Energetická efektivita a cache. Hodně cache

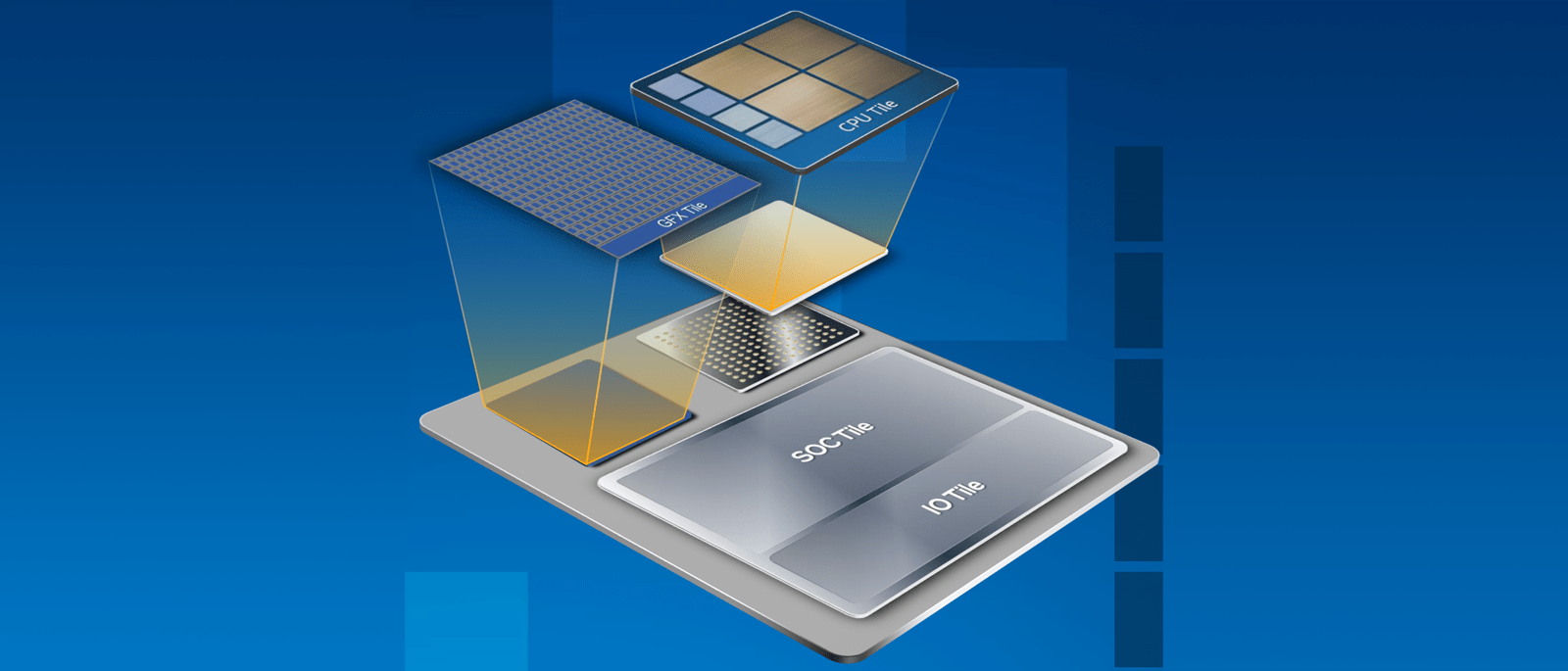

Procesory Tiger Lake (v celém článku bude řeč o Tiger Lake-U, tedy primárně 15W verzi pro úsporná mobilní zařízení) jsou poměrně velkým posunem z hlediska architektury, byť poměrně malým z hlediska konfigurace. Intel i nadále v segmentu 15W procesorů zůstává na čtyřech procesorových jádrech a grafická karta se počtem EU posouvá o (pro Intel docela obvyklých) 50 %, což většinou nepřinášelo nijak výrazný praktický posun herního výkonu. Pro ilustraci: Zatímco AMD za posledních 7 let stále vybavuje integrované grafiky 512 stream-procesory (8 CU), Intel se za stejný interval posunul ze 128 jednotek (16 EU) s Ivy Bridge na 512 jednotek (64 EU) s Ice Lake, tedy na čtyřnásobek, ale dosud výkon řešení AMD nepřekonal, ani jej nedosáhl.

Snad i to přimělo Intel trochu upravit filozofii a namísto dalšího násobení počtu osazených grafických jednotek začal řešit jejich efektivitu a energetickou efektivitu. Především energetická efektivita nebude v rámci Tiger Lake pouze výsadou integrovaného grafického jádra, její vylepšení díky nové verzi 10nm SuperFin procesu zaznamenají i procesorová jádra. Návrh celého čipu byl upraven právě s ohledem na možnosti SuperFin tranzistorů a po dlouhé době se zdá (potvrzení bude na bedrech recenzí), že vývoj výrobního procesu a vývoj architektury tentokrát fungovaly sehraně.

Krom efektivity energetické, díky níž bude architektura schopna dosahovat v rámci 15W TDP výrazně vyšších taktovacích frekvencí a tím i výrazně vyššího výkonu, je podstatným aspektem i efektivita architektury, tedy jaký výkon je možné dostat z daného počtu jednotek nebo z daného (roz)počtu tranzistorů. To velmi úzce souvisí i s IPC, tedy výkonem na jednotku a takt.

Procesorová i grafická jádra mají v tomto ohledu jeden prvek společný. Intel u obou výrazně (až extrémně) navýšil kapacitu cache.

Cache CPU Willow Cove

U procesorových jader nejde jen o navýšení kapacity, ale i o změnu struktury. L2 cache ani L3 cache nejsou inkluzivní, což znamená, že (1) L2 cache nemusí obsahovat data, která se momentálně nacházejí v L1 cache a (2) L3 cache nemusí obsahovat data, která se momentálně nacházejí v L2 cache. Pokud chceme vyčíslit celkovou efektivní kapacitu cache, stačí hodnoty sčítat. Intel dlouho zastával strategii inkluzivní cache, což byla ještě záležitost desktopových a mobilních procesorů Skylake. Změna nastala se serverovým Skylake-X, kdy se L3 stala neinkluzivní (=exkluzivní), což byl důsledek rozhodnutí zvětšit L2 na čtyřnásobek (držet tento obsah navíc i v L3 by neúměrně zvyšovalo nároky na její kapacitu). Všechny desktopové a mobilní deriváty Skylaku (např. Kaby Lake, Whiskey Lake, Coffee Lake, Comet Lake aj.) se držely původního inkluzivního konceptu.

| proces | L1 (dat.+instr.) | L2 | L3 | |

|---|---|---|---|---|

| Broadwell | 14nm | 64 kB (32+32) | 256 kB | 1,5 MB |

| Broadwell-E | 14nm | 64 kB (32+32) | 256 kB | 2,5 MB |

| Skylake | 14nm | 64 kB (32+32) | 256 kB | 2 MB |

| Skylake-X | 14nm | 64 kB (32+32) | 1024 kB | 1,375 MB |

| Canon Lake | 10nm | 64 kB (32+32) | 256 kB | 2 MB |

| Ice Lake | 10nm | 80 kB (48+32) | 512 kB | 2 MB |

| Tiger Lake | 10nm | 80 kB (48+32) | 1280 kB | 3 MB |

U toho zůstaly i nové architektury Cannon Lake (Palm Cove / Skymont) a Ice Lake (Sunny Cove). Pokud tedy (viz tabulka výše) nesl Ice Lake 2 MB L3 cache na jádro, byla efektivní kapacita L3 cache na jádro pouze 1,5 MB, protože zbývající 0,5 MB pouze zrcadlilo obsah L2 cache. Tiger Lake, který koncept inkluzivních cache opouští, tak sice nese 3MB, tedy formálně o 50 % větší L3 cache, ale efektivně je její kapacita 2× vyšší (3 MB vs. 1,5 MB). Podobně je to s L2 cache, jejíž kapacita byla fyzicky navýšena dokonce na 2,5násobek, ovšem efektivně je nárůst ještě mírně vyšší, neboť na rozdíl od Ice Lake neobsahuje L2 cache Tiger Lake také obsah přítomný v L1 cache.

Za pozornost stojí, že se 3 MB L3 cache na jádro dosáhne čtyřjádrový Tiger Lake 12 MB celkové L3 cache, což je trojnásobek kapacity, kterou u čtyřjádrových APU osazuje AMD (4 MB).

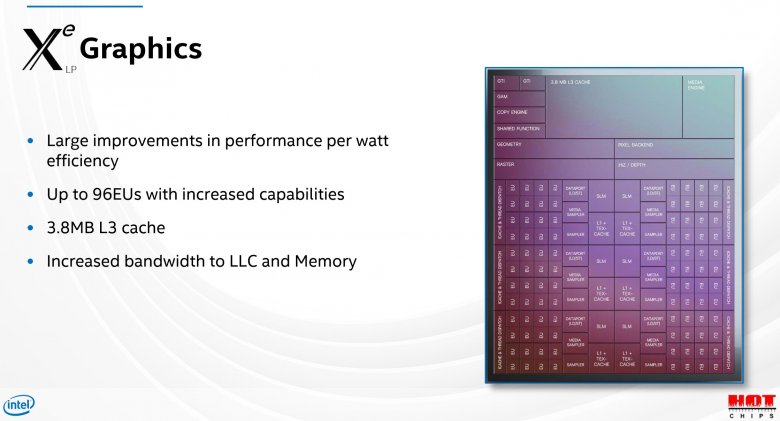

Cache integrovaného GPU

Jak již bylo řečeno, Intel po léta pouze navyšoval počet výpočetních jednotek a upravovaly jejich výbavu, aby odpovídala aktuálním požadavkům na technologickou výbavu, ale příliš neřešil efektivitu. Byli jsme proto svědky případů, kdy zdvojnásobení počtu funkčních jednotek až na pár syntetických testů neodpovídalo posunul reálných FPS, které namísto o násobky stoupaly jen o nižší desítky procent. Intel tak dosáhl stavu, ve kterém se integrované GPU stalo z minoritní části procesoru jeho hlavní složkou a přesto nepřinášelo výkon, který nabízela konkurence (obvykle i za nižší cenu).

Intel sice s Tiger Lake navyšuje počet grafických jednotek z 64 na 96, tedy o 50 %, ale většina výkonu nepůjde na vrub této změně, ale změnám v efektivitě. Jak energetické, díky níž bude grafické jádro v zátěži schopné dosahovat vyšších frekvencí, tak efektivitě na výpočetní jednotku. Jedním z prvků, který k tomu dopomůže, je grafická L3 cache o kapacitě 3,8 MB. Téměř čtyřmegabajtová cache určená čistě potřebám integrované mobilní grafiky je něco nevídaného. Pro srovnání a lepší představu: AMD v současnosti herní grafickou kartu Radeon RX 5700 XT s jádrem Navi 10 vybavuje 4 MB cache poslední úrovně.

S takto objemnou cache se Intel zjevně snaží snížit závislost výkonu na omezené propustnosti sdílené paměťové sběrnice. I ta je však enormně zrychlena a krom klasických DDR4 podporuje i rychlé LPDDR4X-4267 a ještě rychlejší chystané LPDDR5-5400.

Zajímavostí, kterou bychom mohli téma uzavřít, je podpora PCIe 4.0. Zatímco AMD viděla smysl v podpoře PCIe 4.0 v segmentech desktopu a serverů, ale nikoli v mobilním světě, Intel svůj první plně funkční PCIe 4.0 produkt nabídne právě v 15W notebooku. V době vydání však nebude mít využití, neboť současné mobilní grafická řešení od Nvidie (GeForce MAX-Q) PCIe 4.0 nepodporují a na novou generaci na bázi Ampere pro tento segment bude nejspíš potřeba počkat do příštího roku.