Nečekaně odborná prezentace odhaluje procesor AMD Jaguar

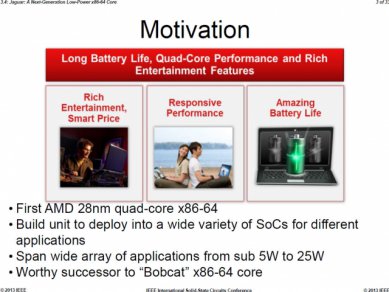

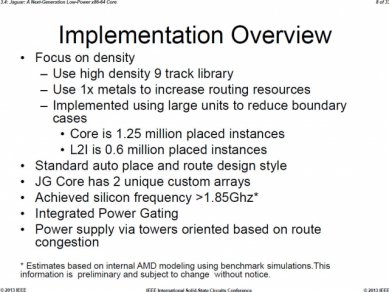

AMD si na letošní IEEE International Solid-State Circuits Conference připravila pětatřicetistránkovou prezentaci na téma procesorového jádra Jaguar, respektive o způsobu implementace této architektury do konkrétní podoby. Když dorazila do naší redakční schránky a začali jsme jí listovat, nepřinesly první stránky žádné překvapení. Opakovaly již známé cíle a parametry tohoto procesoru, což bylo prokládáno tradiční marketingovou grafikou.

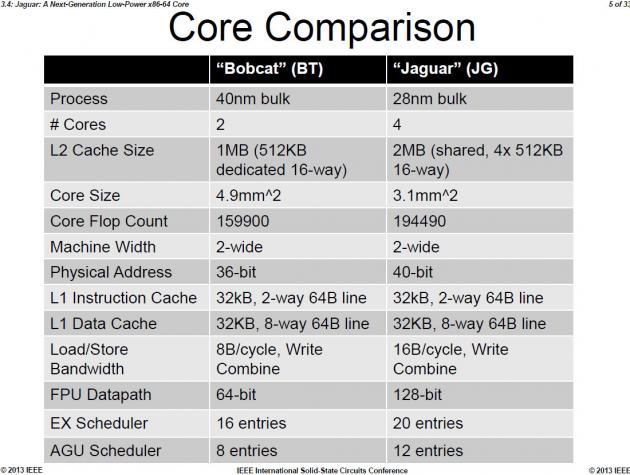

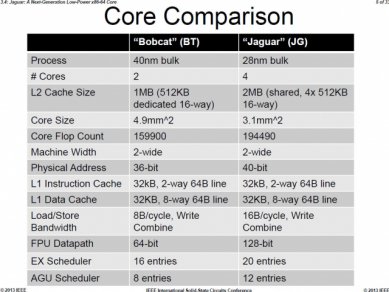

Strany pět a šest už nás trochu překvapily - výčet parametrů a srovnání s generací Bobcat je přece jen o úroveň odbornější, než jsme z podobných prezentací zvyklí.

Při procházení dalších slajdů už jsme dokonce pojali podezření, že se v AMD spletli a poslali nám jiný dokument. Ale není tomu tak. Jen tento dokument nepochází z marketingového oddělení, ale pera inženýrů, čemuž odpovídají zhruba dvě třetiny obsahu. Podíváme se především na onu třetinu, která doplňuje dosud neznámé (nebo jen neoficiální) informace.

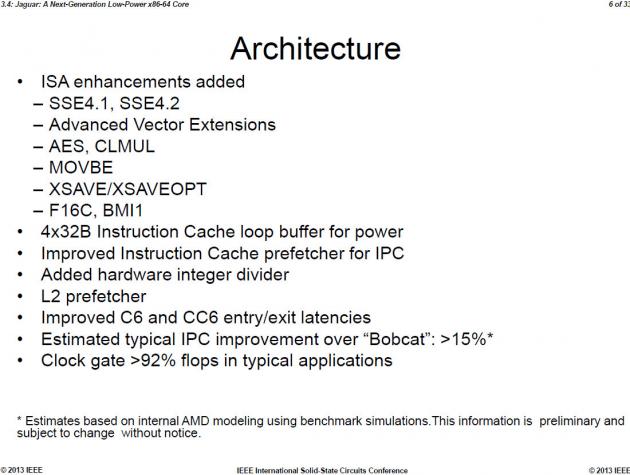

Základním specifikacím jsme se věnovali již v loňském srpnovém článku, takže se z valné části budeme opakovat: Jaguar bude vyráběný 28nm bulkovým procesem (podobně jako stávající grafické čipy) a krom toho oproti Bobcatu přinese četná vylepšení. Čtyřjádrovou konfiguraci (oproti maximálně dvoujádrové), sdílenou L2 cache (tím každé jádro získá přístup k více než 512 KB), menší jádra (3,1 oproti 4,9 mm²), 128bit datové cesty FPU jednotek a s tím související podporu pro 256bit AVX instrukce.

Krom již známé hardwarové jednotky pro dělení (která podle starších zpráv byla převzata z architektury K10.5) stojí za zmínku i L2 cache prefetching, který by měl snížit čekací doby jádra na přenosy dat (laicky jej můžeme charakterizovat Trautenberkovským „nečekat, nestát, dělat“ :-). AMD potvrzuje minimálně o 15% vyšší IPC ve srovnání s Bobcatem.

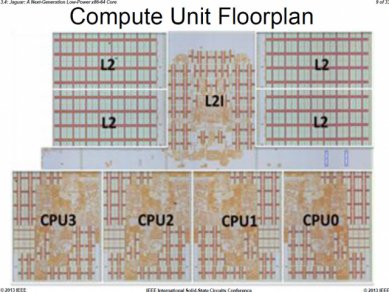

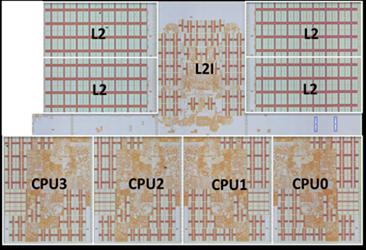

AMD Jaguar - čtyřjádrový modul s L2 cache

Zajímavý je die-shot samotného Jaguaru. AMD totiž celek čtyř jader se čtyřmi sdílenými 512bit bloky L2 cache a komunikačním rozhraním prezentuje jako „compute unit“, tedy jakousi základní jednotku, která by měla být základem všech produktů s jádry Jaguar. Připadá nám, že zřejmě ani žádná nativní dvoujádrová varianta Jaguaru existovat nebude a veškeré dvoujádrové modely budou vycházet z deaktivovaných kousků.

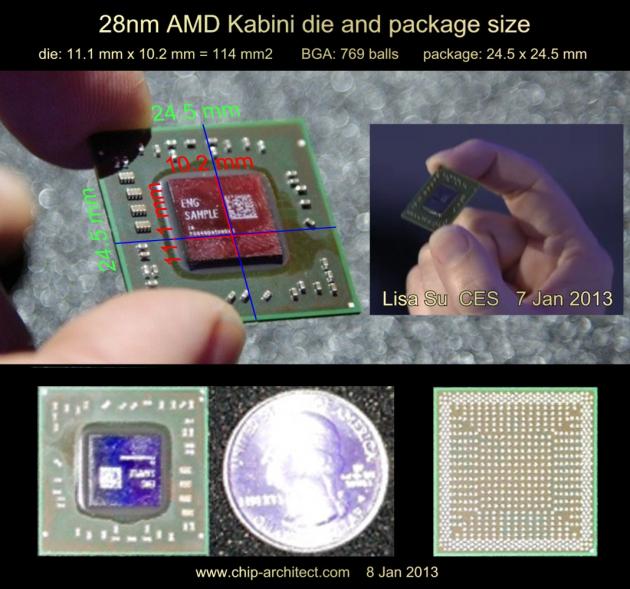

Ať už se tak stane nebo ne, dostačuje nám snímek Jaguářího modulu a rozměr jednoho jádra k tomu, abychom pomocí grafického editoru a trojčlenky dopočítali rozměry celého modulu (tzn. čtyř jader, L2 cache a rozhraní) - vychází nám přibližně na 26 mm². Můžeme ale počítat dál. Známe totiž i přibližné rozměry Kabini (obrázek výše), jednoho z APU, které Jaguar ponese. To podle měření webu Chip Architect dosahuje zhruba 114 mm², což znamená, že procesorová část tvoří necelých 23 % plochy APU. Zhruba 3/4 čipu pak spadá na grafické jádro, řadič, čipset a všechna možná I/O rozhraní.

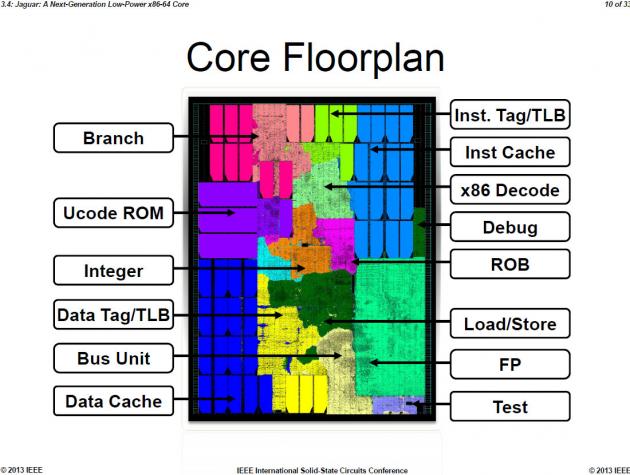

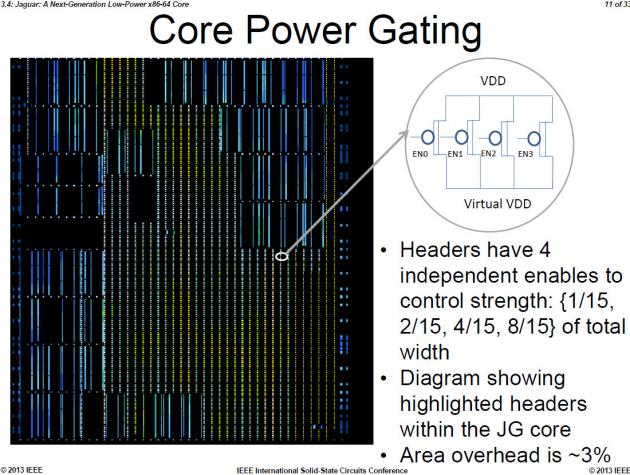

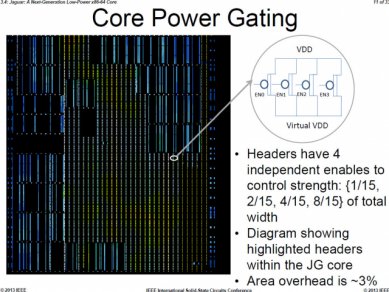

AMD se pochlubila i rozvržením jednotlivých částí jádra (výše vlevo) a implementací technologie power-gating (vpravo), která na úkor 3% zvětšení jádra zaručí nižší energetické nároky všech částí, které nejsou v daný okamžik plně vytížené.

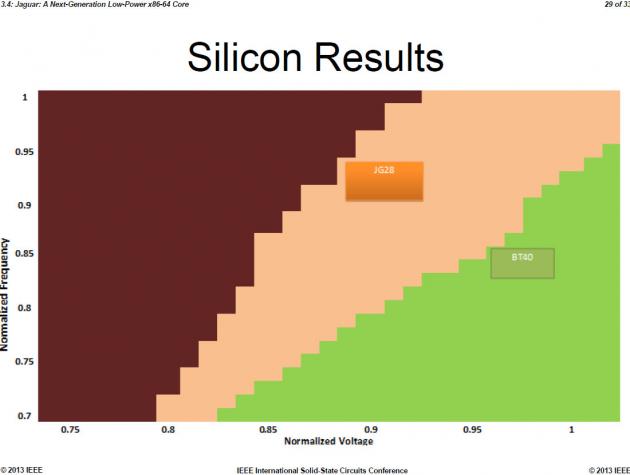

Závěrem se zastavíme u grafu, který nás informuje o závislosti dosažitelné frekvence na napětí pro 28nm Jaguar (JG28) ve srovnání se 40nm Bobcatem (BT40). Při napětí mezi 0,9 a 0,95 V dosahuje Jaguar o 20 % vyšší frekvence (což je podobný nebo o chlup lepší výsledek ve srovnání s nástupem 28nm grafických čipů).

Všechny stránky prezentace včetně odborných schémat najdou případní zájemci níže v galerii.

AMD (e-mail)