Pohled do nitra mikroarchitektury K8L

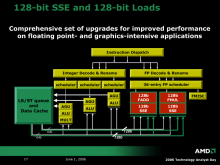

Jelikož jsou Opterony zaměřeny převážně na práci, která dost často využívá operací v plovoucí řádové čárce, snažili se vývojáři v AMD zapracovat právě na této stránce procesoru. A protože software již asi tak desítku let směřuje k využívání SSE (Streaming SIMD Extensions), nemůžeme nenalézt vylepšení právě zde. Přehled základních změn s SSE je shrnut v tabulce.

|

Možná vám to bude připomínat změny v architektuře Intel Core oproti NetBurstu a třeba vás též napadne, zda AMD od Intelu neopisuje. My si naopak myslíme, že jde spíše o logický vývoj.

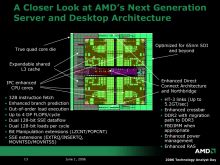

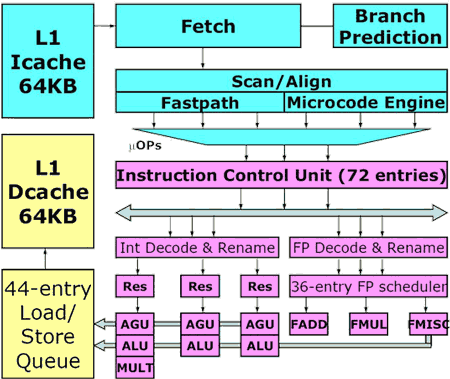

Další vylepšení se týkají efektivity zpracovávání instrukcí za takt. Patří mezi ně „advanced branch prediction“ či „Out-of-order load execution“ pro minimalizaci relativně vysoké latence L2 cache.

Když už jsme u té cache procesoru, sluší se zmínit jednu věc, kterou už možná znáte. L1 a L2 cache jsou v procesorech AMD tzv. „exclusive“, což znamená, že v L2 cache není kopie L1 tak, jako je tomu v procesorech Intel. Jednotlivá jádra K8L budou mít 64 kB L1 a 512 kB L2 cache, což se prakticky od současného stavu moc neliší.

Výraznou změnou však bude cache třetí úrovně (L3 cache), kterou budou všechna jádra sdílet. V procesorech architektury Intel Core se sdílí mezi jádry rovnou L2 cache. Návrh K8L procesoru navíc umožňuje v případě potřeby L3 cache rozšiřovat (ne tak už L2 či L1 cache).

Drobných vylepšení dozná také virtualizační technologie. Narozdíl od současných procesorů, kde se pro virtualizaci hardwaru využívá „stínového stránkování“ (shadow paging) bude K8L virtualizované adresy rovnou překládat, čímž se urychlí práce hypervisora, který má na starosti správu podřízených operačních systémů a zejména pak obsluhu virtualizovaného hardwaru.

Na letním AMD Analyst Day se také hovořilo o vylepšené správě napájení, což má být další klíčový prvek K8L. Doposud se na základě požadavků na vytížení taktoval celý procesor, nyní bude možné řídit rychlost jednotlivých jader nezávisle.

Podobně na tom bude i paměťový řadič, jehož rychlost bude záviset na požadavcích od systému. Aplikace může třeba požadovat velký datový rok, ale málo procesorového času, pracovat tak bude především paměťový řadič a procesory budou „relativně“ odpočívat. Anebo tomu může být naopak a paměťový řadič nepojede naplno, neboť to nebude třeba. Samozřejmě není vyloučena ani situace, kdy bude potřeba obojího. Počítá se tedy s regulací napětí zvlášť pro paměťový řadič a zvlášť pro jádra (tam už však nebude regulace napětí jader nezávislá, jako jejich frekvence). Celý procesor se má se spotřebou ve standardním provedení vejít do 95 W. Příklad, který AMD uvádí, je sestava o dvou čtyřjádrových procesorech, k tomu paměti a čipset (neboli základní deska) a to se bez datového úložiště a grafiky má vejít do 240 W.