V-cache pro Zen 5 bude „odlišná“

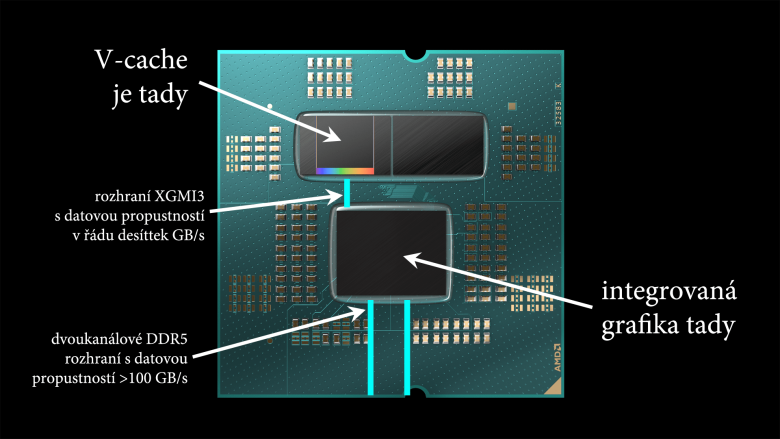

AMD nasadila technologii V-cache s generací Zen 3, poté se Zen 4 její využití rozšířila i na PC procesory s vyšším počtem jader. V obou případech jde o navrstvení křemíku nesoucího 64 MB SRAM na procesorový čiplet, který obsahuje 32 MB SRAM využívaných jako L3 cache. V-cache tuto kapacitu ztrojnásobí. Z toho profitují některé profesionální aplikace, v PC segmentu však zejména hry.

Lze očekávat, že ani se Zen 5 to nebude jiné a ačkoli AMD donedávna o modelech s V-cache nehovořila, očekává se jejich vydání načasované jako reakce na procesory Intel Arrow Lake. Patrně koncem letošního či začátkem příštího roku, s největší pravděpodobností začátkem ledna 2025 na CES.

K X3D [V-cache] toho máme hodně co říct. Rozhodně neusínáme na vavřínech. Zlepšujeme to, co lze s X3D dělat, je to opravdu zajímavé a já se moc těším, až si o tom s vámi popovídáme. [...] Není to jako: hele, přidali jsme na čip X3D. Aktivně pracujeme na zajímavých odlišnostech, aby to bylo ještě lepší. Pracujeme na X3D, vylepšujeme ho. --- Donny Woligroski, AMD |

V rozhovoru pro PCGamer potvrdil přípravu procesorů Ryzen 9000X3D Donny Woligroski z AMD. V-cache pro tuto řadu má být v nějakých ohledech odlišná než stávající, což vyvolalo vlnu spekulací na téma, co by vlastně AMD mohla v rámci možnosti stávajících technologií vylepšit či rozrůznit.

Popsané schéma využití V-cache na Ryzen 7000X3D (DIIT)

Jako celkem reálné se jeví dvě možnosti. Buďto snížení rozdílu mezi takty standardních čipletů a čipletů osazených V-cache, nebo nabídku V-cache o různé kapacitě.

Po technologické stránce připadají v úvahu i další možnosti; otázkou je, zda by jejich přínos zvládal vykompenzovat nárůst nákladů. Tak třeba by hypoteticky bylo možné osadit V-cache na centrální čiplet a vytvořit jakousi L4 cache o vyšší kapacitě. Výhodou by byla její dostupnost pro oba procesorové čiplety a eliminace současného poklesu taktů. Nevýhodou potřeba centrálního čipletu vybaveného rozhraním pro V-cache.

Jako další možnost mne napadá umístění procesorových čipletů na křemíkovou podložku, která by SRAM integrovala. Tam by nebylo potřeba vyvíjet nové čiplety (čiplety vybavené rozhraním pro křemíkovou podložku AMD chystá pro APU Strix Halo, které se právě na začátek roku 2025 chystá a které právě s integrací cache poslední úrovně počítá), ale navýšilo by to náklady o cenu podložky. Výhody by ale byly zřejmé: (1) Žádná degradace taktovacích frekvencí, (2) cache dostupná pro oba procesorové čiplety, (3) oproti cache na centrálním čipletu podstatně rychlejší rozhraní mezi CPU jádry a cache poslední úrovně). Jde de facto o řešení, které se v desktopu očekávalo až se Zen 6, takže je otázkou, zda jej AMD bude chtít využít takto (řekněme) s předstihem. Zajímavé, odlišné a vylepšené by to však bylo bezpochyby.