AMD hovoří o sdílené FPU v Bulldozeru: „Flex FP“

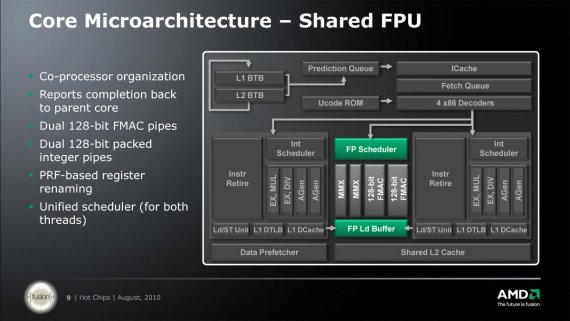

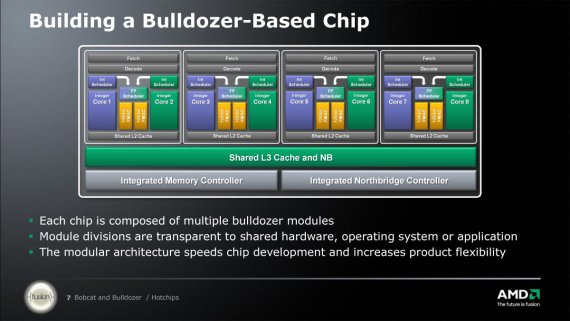

„Flex FP“ v „Bulldozeru“ bude opravdu „flexibilní“. Zatímco dnes je běžné, že každé jádro obsahuje jednu FPU, v „Bulldozeru“ bude jedna FPU na dvě jádra, takže 16jádrový „Interlagos“ bude mít osm „Flex FP“. Každá „Flex FP“ dostane vlastní „scheduler“ (plánovač operací), nebude tak závislá na scheduleru jednotky pro celočíselné operace („Integer unit“) a nepotřebuje zdroje této jednotky ani pro plánovaní 256bitových operací, takže lze „Flex FP“ plně vytížit (Fruehe dodává, že konkurenční architektury měly společný scheduler jak pro celočíselné operace, tak pro FPU).

Jedna z nových instrukčních sad, která umí využívat 256bitové operace v plovoucí řádové čárce, je AVX (celkem 12 nových instrukcí). Malá odbočka: Intel přijde s AVX v procesorech Sandy Bridge, výkon AVX demonstroval letos na IDF (orientačně jde o až dvakrát rychlejší zpracování v porovnání se současnými možnostmi různých SSE rozšíření). Pochopitelně neexistuje něco jako „256bitový příkaz“, tzv. „single precision“ příkazy jsou 32bitové (přesněji pracují s 32bit. operandy) a „double precision“ jsou 64bitové. Je-li tedy „FPU 128bitová“, znamená to, že tyto „128bitové příkazy“ jsou vykonávány jako čtyři „single precision“, nebo dva „double precision“, to vše v jednom cyklu (taktu procesoru). AVX toto dále znásobí (zvládne za jeden cyklus udělat osm 32bit., nebo čtyři 64bitové operace), pochopitelně musí to umět využívat aplikace. Pokud to aplikace neumí, vykonává zmíněné „128bitové“ příkazy a z FPU navržené pro práci s „256bitovými“ ždímá „polovinu potenciálu“.

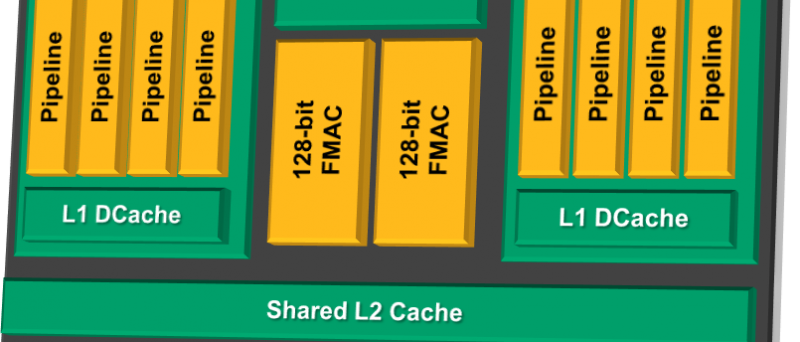

S „Flex FP“ je to trochu jinak. Obsahuje totiž dvě 128bit. FMAC jednotky, každá zvládá vykonat „128bit. příkaz“ za jeden cyklus (umí dělat FMAC, FADD, nebo FMUL). „Flex FP“ je však možné využít i pro zpracování „256bit.“ příkazů, tedy pro vykonávání např. instrukcí ze sady AVX. V takovém případě může jedno jádro využít obě 128bit. FMAC jednotky a provést během jediného cyklu „256bit. příkaz“. Co když ale druhé jádro bude chtít udělat totéž?

Většina výpočtů v datových centrech dnes spoléhá na celočíselné operace, menší část potřebuje pracovat s plovoucí řádovou čárkou. Plnohodnotná 256bitová FPU na každé jádro tak představuje „plýtvání křemíkem“, protože by se většinu času nečinně válela a spotřebovávala energii. Ušetřené místo snížením FPU na polovinu se tak dá využít efektivněji, lze třeba přidat další jádra. Je málo pravděpodobné, že druhé jádro modulu „Bulldozer“ bude v daný moment také potřebovat FPU a provádět „256bit. příkaz“. Obě jádra současně však mohou provádět jeden „128bit. příkaz“ („Flex FP“ obsahuje dvě 128bit. FMAC a každou je možné přidělit jednomu jádru pro daný cyklus). Pokud by obě jádra naráz potřebovala udělat „256bit. příkaz“, bude to prostě trvat dva cykly. Pravděpodobnější bude, pokud nebudou další jádra zaměstnána, že se o to postará další FPU z jiného „Bulldozer“ modulu. Beztak ale procesor provádí mezitím další celočíselné operace, takže pravděpodobnost těžkého zaměstnání všech FP jednotek je v takové situaci poměrně malá.

Je tedy zjevné, že modul „Bulldozer“ nebude úplně ideálně navržen pro masivní paralelní provádění 256bit. instrukcí. Však také AMD hodlá „Flex FP“ nasadit spíše coby dočasné řešení, které ale za stávající situace může mít smysl (kdo ví, třeba AMD později přenechá zpracování AVX a nadcházejících „silnějších“ instrukcí grafické části APU, tedy nejdříve asi v nějakých novějších generacích, v té prvotní by pravděpodobně narazili na solidní latence). Přitom se procesor krásně vejde do současné spotřeby i při zvyšování počtu jader. Intel bude mít v „Sandy Bridge“ pro každé jádro vlastní 256bit. jednotku (tvořenou také poměrně efektivním způsobem, ale to by bylo nad rámec tohoto článku), takže se dá předpokládat, že špičkově bude schopen 8jádrový „Sandy Bridge“ procesor zhruba dvojnásobně rychlého zpracování 256bit. instrukcí v porovnání s 8jádrovým „Bulldozerem“ (ten bude mít totiž jen polovičku FPU). Realita bude ještě hodně záviset na konkrétní implementaci a pochopitelně také na tom, jak moc bude potřeba zaměstnávat FPU 256bit. AVX instrukcemi. Zde se názory Intelu a AMD liší, Intel pro AVX dělá hodně, AMD to zase tolik žíly netrhá.