AMD má již v laboratoři funkční vzorek 64jádrového Zen 5

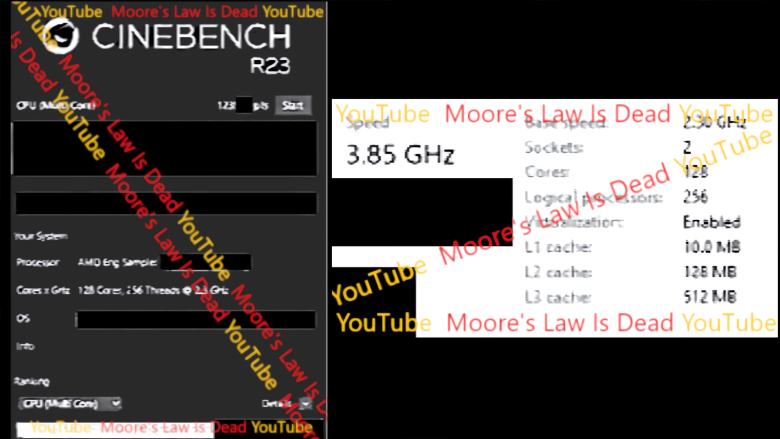

S informací přišel YouTube kanál MLID, který zveřejnil částečně cenzurovaný screenshot výsledku tohoto procesoru v testu CineBench R23. Dvojice těchto vzorků v něm dosahuje 123 tisíc bodů, což nám samo o sobě nic moc neřekne, protože ve stávající podobě (bugfixing, takty) bude mít procesor k finální podobě daleko.

Dozvídáme se nicméně několik zásadních informací: Vzorek Zen 5 je funkční, dokáže stabilně dokončit test CineBench R23, existuje ve 64jádrové konfiguraci schopné fungovat ve dvou socketech, má nastaven základní takt 2,30 GHz a boost 3,85 GHz. Na jakém taktu reálně běžel, je samozřejmě otázka.

CineBench R23 detekuje celkem 10 MB L1 cache, 128 MB L2 cache a 256 MB L3 cache. 10 MB L1 cache při 128 jádrech znamená kapacitu 80 KB pro každé:

| cache | L1 | L2 | L3 | ||||

|---|---|---|---|---|---|---|---|

| data | inst. | BTB | na jádro | TLB | na jádro | konf. | |

| Zen | 32 kB 4-way | 64 kB | 512e | 512 kB | 1536e | 2 MB | [8]+[8] |

| Zen 2 | 32 kB 8-way | 32 kB | 512e | 512 kB | 2048e | 4 MB | [16]+[16] |

| Zen 3 | 32 kB 8-way | 32 kB | 1024e | 512 kB | 2048e | 4 MB | [32] |

| Zen 3 +V-cache | 32 kB 8-way | 32 kB | 1024e | 512 kB | 2048e | 12 MB | [32+64V] |

| Zen 4 | 32 kB 8-way | 32 kB | 1536e | 1024 kB | 3072e | 4 MB | [32] |

Zen 4 | 32 kB 8-way | 32 kB | 1536e | 1024 kB | 3072e | 12 MB | [32+64V] |

| Zen 5 | 80 kB | ? | 1024 kB | ? | 4 MB | [32] | |

Ze samotné hodnoty nicméně není možné určit, jak tato kapacita bude rozdělena mezi datovou a instrukční část L1 cache (tedy například zda půjde o kombinaci 40 + 40 kB, 32 + 48 kB ap.).

Kapacita L2 cache zůstává přinejmenším v této konfiguraci Zen 5 (tj. 8jádrové 4nm CCD) stejná jako u Zen 4, tzn. 1 MB na jádro. V tomto ohledu se objevovaly vzájemně si odporující informace o jistém (ne)navýšení, případně o (ne)změnění struktury L2 cache. Problém bude nejspíš v tom, že jádro Zen 5 bude existovat v řadě vydaných konfigurací (a řadě experimentálních nevydaných), takže každý zdroj mohl hovořit o jiné.

L3 cache zůstává 4 MB (na jádro) a v jejím případě se ani žádná změna neočekávala. AMD od Zen 3 využívá V-cache, takže nejspíš vnímá jako ekonomičtější navyšovat kapacitu L3 jen v těch segmentech, kde to má s ohledem na cílovou zátěž dopad na výkon.