CES 2011: VIA uvádí dvoujádrový procesor VIA Nano X2 na 40nm technologii

O VIA Nano X2 již víme prakticky vše, kromě konkrétních modelů a jejich taktů, o těch se VIA zatím nezmiňuje (dříve předváděný 65nm vzorek běhal na 1,8 GHz, počítáme, že nyní to bude podobné, pouze se adekvátně sníží spotřeba, o níž VIA ovšem nyní v souvislosti s VIA Nano X2 také mlčí). Procesory VIA Nano X2 nicméně obsahují všechny důležité technologie. Kromě dvou jader je to podpora 64bitového rozšíření (pochopitelně kompatibilní s AMD64), virtualizační technologie, SSE instrukce až po SSE4 (ty se prvně u VIA objevily v Nano řady 3000) i pomocné instrukce pro šifrování (AES) a hashování (SHA-1, SHA-256) v podobě VIA PadLock Engine.

O VIA Nano X2 již víme prakticky vše, kromě konkrétních modelů a jejich taktů, o těch se VIA zatím nezmiňuje (dříve předváděný 65nm vzorek běhal na 1,8 GHz, počítáme, že nyní to bude podobné, pouze se adekvátně sníží spotřeba, o níž VIA ovšem nyní v souvislosti s VIA Nano X2 také mlčí). Procesory VIA Nano X2 nicméně obsahují všechny důležité technologie. Kromě dvou jader je to podpora 64bitového rozšíření (pochopitelně kompatibilní s AMD64), virtualizační technologie, SSE instrukce až po SSE4 (ty se prvně u VIA objevily v Nano řady 3000) i pomocné instrukce pro šifrování (AES) a hashování (SHA-1, SHA-256) v podobě VIA PadLock Engine.

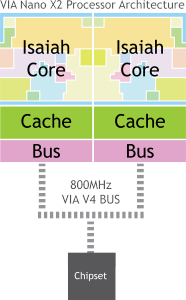

Jak už jistě víte, procesory vycházejí z mikroarchitektury „Isaiah“ použité i v prvních VIA Nano, obě jádra mají vlastní L2 cache (tipujeme 1 MB na jádro), není zde žádná L3 cache, jádra spolu komunikují přes sběrnici (800MHz VIA V4 Bus), kterou jim poskytuje čipset. Procesory jsou pinově kompatibilní s předchozími VIA Nano i C7/Eden/atd…, takže pro výrobce bude tvorba nových desek snadnou záležitostí (prostě tam začnou dávat jiné čipy a upraví BIOS).

No, a to je od nás vše, více vám k tomu jistě v diskuzi řekne Tralalák (že necháme děkovat ;-).