Jak se Zen 5 vešel na plochu Zen 4? AMD zhustila L3 a rozhraní V-cache

Nedozvídáme se to od AMD, ale díky společné práci fotografa Fritzchens Fritz (který připravil mikrosnímek křemíku Zen 5 o velikosti 1,6GB složení z tisíců mikroskopických snímků) a analýze YouTube kanálu High Yield, který provedl porovnání se snímky Zen 4.

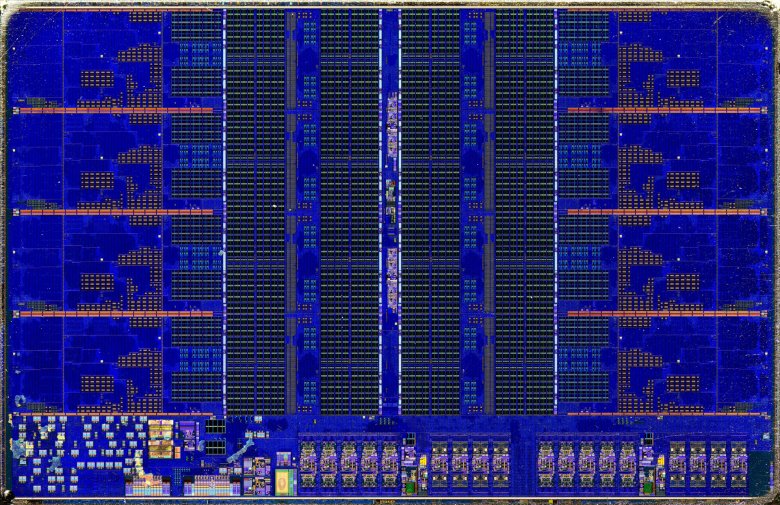

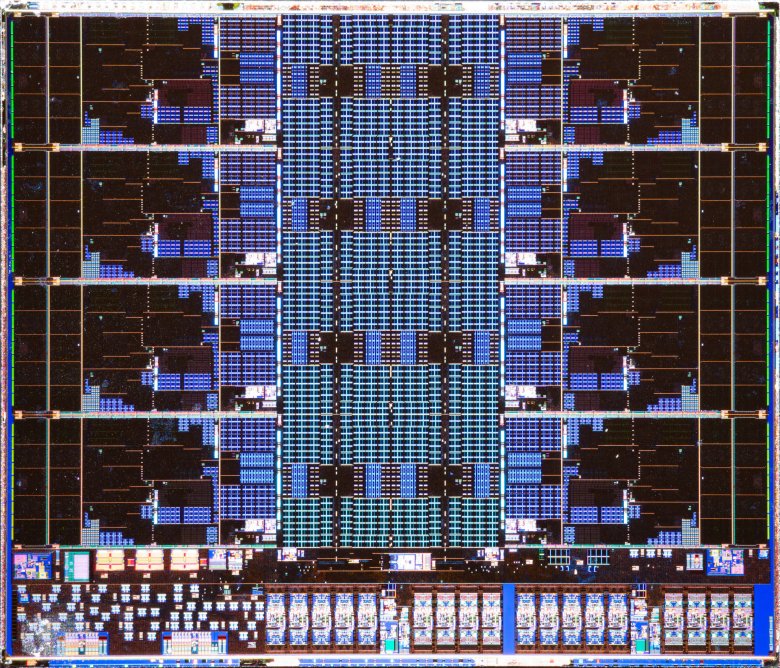

Zen 4 CCD (vlevo), Zen 5 CCD (vpravo), (Fritzchens Fritz, CC0)

CCD (čiplet) Zen 4 a Zen 5 mají totožnou plochu ±1 % (rozdílem velikosti snímků výše se nenechte zmást, redakční systém prostě dvojici obrázků vymezí vždy polovinu šířky stránky). Liší se sice poměrem stran (Zen 4 CCD je obdélníkovější, Zen 5 CCD je čtvercovější), ale výsledná plocha je s rozdílem několika desetin milimetru totožná.

Dosud nebylo jasné, jak se toho AMD podařilo dosáhnout, když počet tranzistorů stoupl z 6,57 miliardy na 8,315 miliardy. Proces přitom prakticky nepomohl, 4nm technologie TSMC je derivátem 5nm a plochu snižuje o kosmetických 6 %. Zde však bylo potřeba zmenšení o 21 %, aby se 8,315 miliardy tranzistorů Zen 5 vměstnalo na stejnou plochu jako 6,57 miliardy tranzistorů Zen 4. Kde AMD plochu ušetřila?

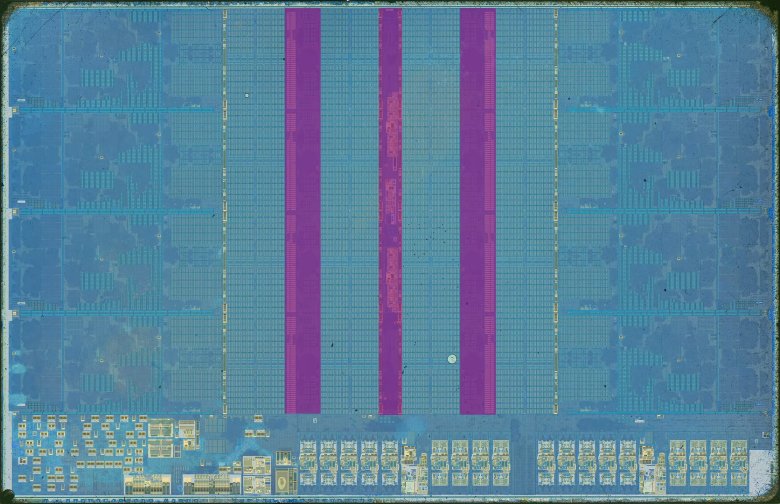

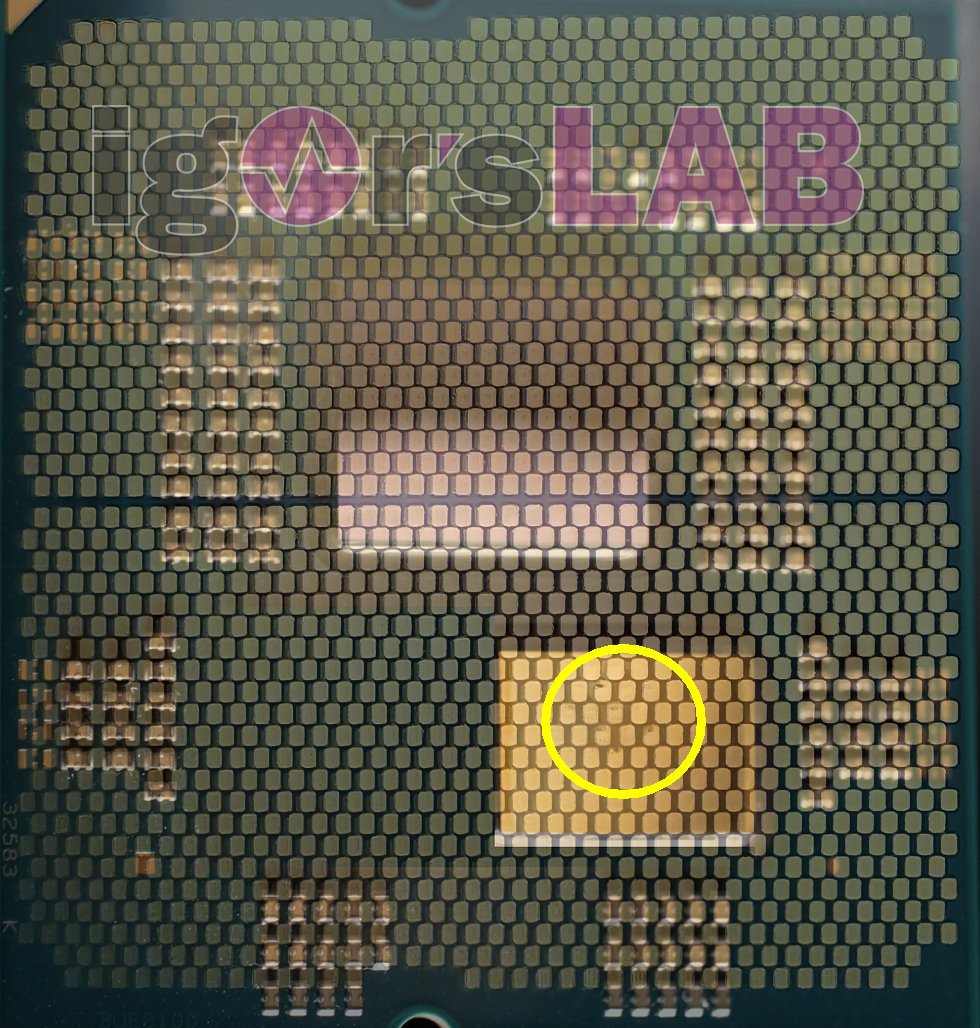

Nápadně klesla plocha, na které se rozkládá L3 cache. Když se podíváte na modrý snímek vlevo (Zen 4), je středová část čipletu věnována právě L3 cache (ze stran je lemovaná bílou „přerušovanou čárou) a zleva a zprava L3 cache jsou jednotlivá jádra Zen 4. U Zen 5 (vpravo) tvoří centrální plocha s L3 cache poměrově menší část jádra než plocha s jádry. Samotné L3 cache přitom zůstává 32 MB a kupodivu se nijak nezměnila velikost jednotlivých datových buněk. Co se změnilo, je situace mezi buňkami. U Zen 4 (vlevo) si můžete všimnout, že plochu s L3 cache protínají tři svislé (modré) pruhy. Středový pruh obsahuje malé množství nějaké logiky, zbývajícími dvěma pruhy procházejí datové a napájecí cesty pro V-cache (TSV). Na snímku níže jsou pro lepší názornost tyto pruhy zvýrazněny fialově:

Zen 4 CCD (High Yield)

U Zen 5 zmizel středový pruh prakticky zcela a pruhy s rozhraním pro V-cache byly extrémně zredukovány. Kupodivu nejen co do plochy, ale především co do počtu spojů (TSV). Zatímco Zen 3 CCD nesl přes 24 tisíc TSV a Zen 4 CCD tento počet jen nepatrně snížil, v případě Zen 5 CCD jsou TSV nejen menší, ale především je jejich počet redukován na zhruba 9 tisíc.

Jak vysvětlit, že k realizaci datově stejně širokého spojení najednou stačí téměř třetina spojů a jak vysvětlit, že jednotlivé spoje mohou být podstatně menší, zatím nevíme. Lze spekulovat, že první generace nesly velké množství redundantních spojů, aby v případě chybného spojení některého z nich byla výtěžnost spojování vrstev stále vysoká a nyní došlo k vyladění technologie, takže vysoká redundance není potřeba. Důvody mohou být ale i zcela jiné, neznámé.

Nejde však o jedinou záhadu. Se zmenšením plochy L3 cache a zvětšením plochy jader Zen 5, by při použití klasické V-cache byla touto V-cache překryta i docela podstatná plocha procesorových jader. Což by znamenalo potřebu snížení taktů, aby nedocházelo k přehřívání. Přitom se očekává, že Zen 5 s V-cache naopak bude co do frekvencí méně penalizován než Zen 4 s V-cache. Opět lze jen spekulovat: Nová V-cache může podstatně lépe odvádět teplo, nebo dojde k použití dvouvrstvé V-cache a tím snížení její plochy (takže nebude překrývat jádra vůbec - tedy ještě méně než u Zen 4 - pouze L3 cache). Nebo je tu ještě něco jiného, co nám zatím uniká.