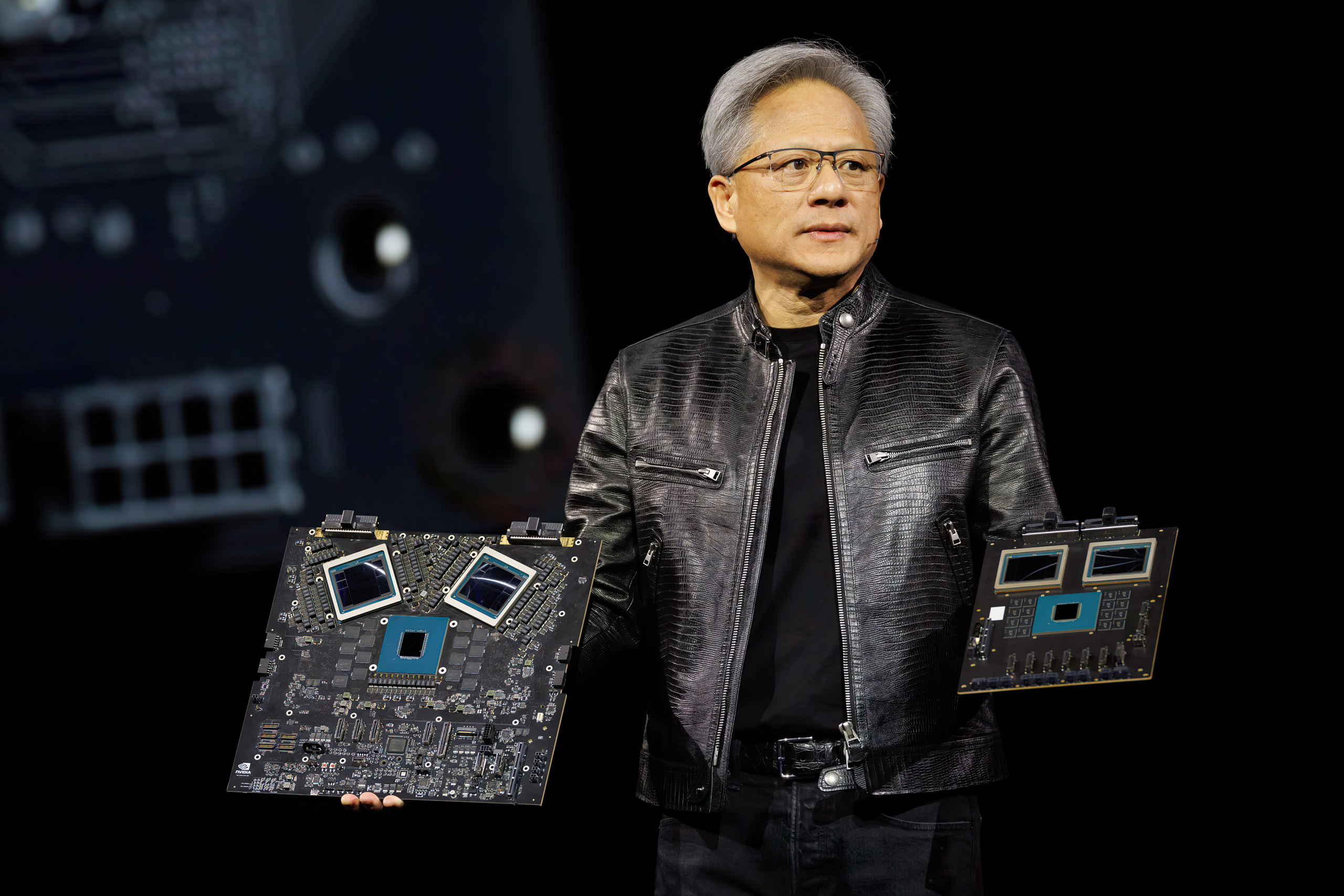

Nvidia Ampere: 1. září, Intel Tiger Lake: 2. září

Odpočet Nvidie „za 21 dní po 21 letech“, který lákal na explozivní událost (souvislost s Bejrútem bude jistě čistě náhodná) poukazoval na den D 31. srpen. Jenže, jak Nvidia později upřesnila, půjde o 1. září. Holt, časová pásma dělají své a když je na jedné polokouli pondělí, může být na druhé již úterý. Odhalení herního Amperu si tam můžete poznačit do kalendáře na první školní den, úterý 1. září.

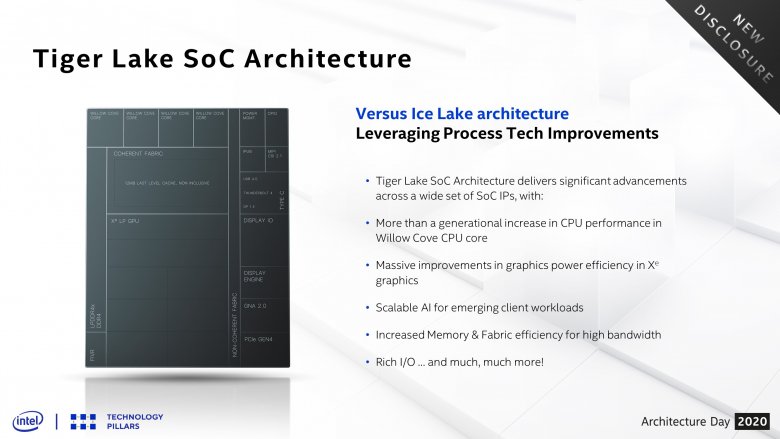

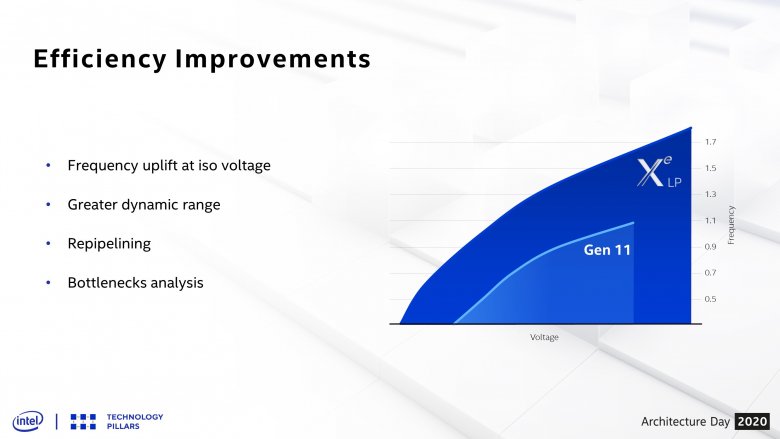

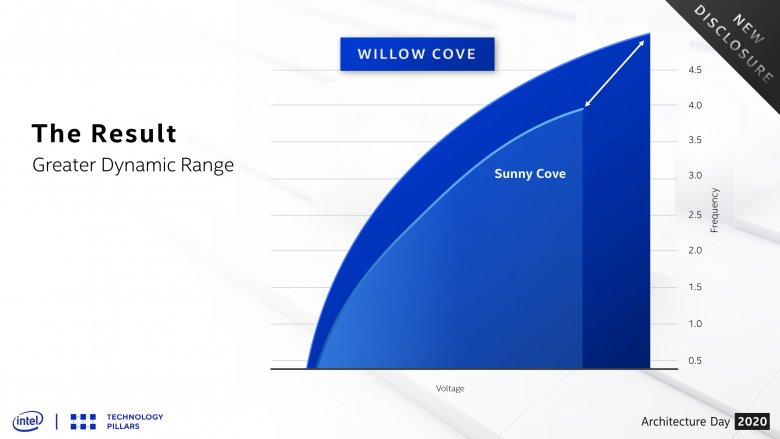

Hned ve středu 2. září bude následovat Tiger Lake od Intelu. K tomu se objevila řada zajímavých informací. Krom již známých faktů, tedy že půjde o novou architekturu Willow Cove s vyšším IPC (i díky 1,5× větší L1 data cache, 2,5× větší L2 cache a 1,5× větší L3 cache), se dozvídáme zajímavé novinky o třetí generaci 10nm procesu. Ten bude mít zcela přepracované tranzistory, které Intel označuje jako SuperFin a nové kondenzátory Super MIM. Díky těmto změnám třetí generace dosahuje 5× vyšší kapacitance a o 30 % nižšího odporu. Intel rozdíly přirovnává k mezigeneračnímu posunu.

To ostatně naznačují i posuny frekvencí, které se týkají jak maximální dosažitelné frekvence, která se bude alespoň blížit potenciálu 14nm procesu, tak základních taktů, k jejichž zvýšení je potřeba výrazný posun v energetické efektivitě procesu (údaj o posunu z 1,2 GHz na 3,0 GHz pro dvoujádrové Core i3 mezi generacemi Ice Lake a Tiger Lake vypovídá o mnohém).

Protože procesorová jádra s vyšším IPC a vyššími takty, ostatně i výkonnější integrovaná grafika, budou potřebovat lepší zásobování daty, zdvojnásobil Intel přenosovou kapacitu sběrnice ring-bus, zvětšil cache všech úrovní (což už bylo zmíněno) a rozšířil podporu pamětí kompatibilních s rozhraním řadiče na spektrum od DDR4-3200 přes LPDDR4x-4677 až po LPDDR5-5400.