Rambus hodlá dosáhnout přenosu dat 1 TB/s

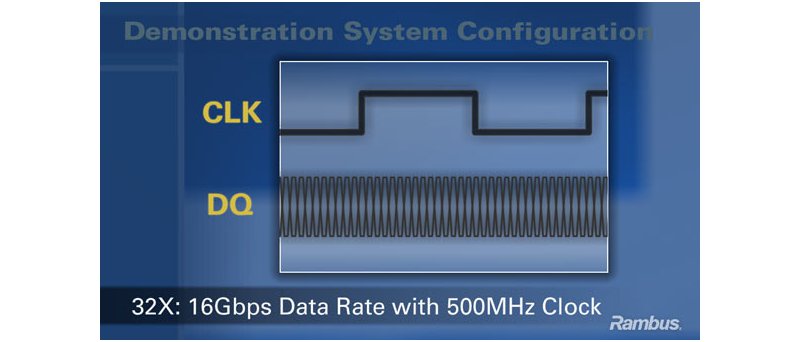

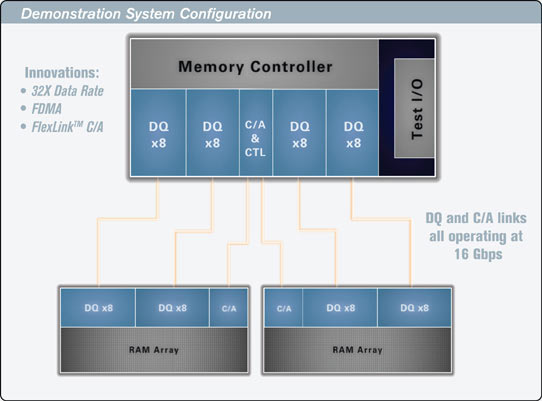

Základem Rambusovy Terabyte Bandwidth iniciativy je mimo jiné 32× data rate, což když porovnáte s DDR (Double Data Rate), zjistíte, že je už samo o sobě 16krát rychlejší. Ano, Rambus chce skutečně během jednoho hodinového cyklu přenášet 32 datových bitů (pro základy funkčnosti SDR, DDR a DDR2 se letmo mrkněte na náš starší článek), což mu právě umožní při 500MHz pamětech dosáhnout datového toku 16 Gbit/s (tedy zmíněné 2 GB/s).

32×DR je samozřejmě jen začátek, nezbytná je také FDMA, tedy použití rozdílových signálů jak pro data, tak i příkazy a adresování. A právě pro příkazy a adresování (C/A) je tu další oddělená cesta s názvem FlexLink C/A.

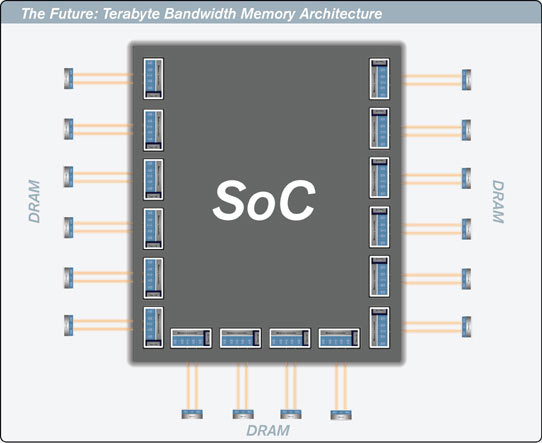

Toto a ještě pár dalších vychytávek, jako je zvýšení integrity signálů nebo z XDR vám již známé FlexPhase pro precizní sladění všech signálů v cílovém čipu, by mělo vést k vytvoření čipu, který po připojení šestnácti DRAM, každý komunikující o rychlosti 16 Gbit/s přes rozhraní o šířce bajtů, dosáhne celkové datové propustnosti 1 TB/s.

Veškeré použité technologie má pochopitelně Rambus buďto již patentovány, nebo čekající na schválení na patentovém úřadě. Celá tato terabytová iniciativa už čítá celosvětově na tisícovku patentů. Jen škoda, že zatím nevíme, kdy bychom se měli dočkat nějakého reálného se zjevení této technologie na trhu.