Zen 6 přinese AVX512_FP16 a 6× INT scheduler

Procesory generace Zen 6 nabídnou mimo jiné až 24 jader na socket, 2nm výrobní proces nebo podporu nových instrukcí včetně AVX512_FP16, což byl poslední prvek, který procesorům AMD scházel k dosažení plné podpory AVX10 od Intelu.

V kontextu Zenu 6 se ale mluví hlavně o efektivitě paměťového subsystému. Tak například kapacita L3 (na čiplet) bude navýšena ze stávajících 32 MB na 48 MB. Spojení mezi procesorovými čiplety a centrálním čipletem již bude přímé (křemík-křemík), nikoli přes pouzdro, takže odpadne rozhraní SERDES, čímž se zredukují latence. Centrální čiplet bude nový, vyrobený pokročilejším procesem a obsahující nový řadič DDR5, takže bude podporovat vyšší takty a nižší latence. Pro modely X3D byla vyvinuta nová V-cache, která zvyšuje kapacitu ze stávajících 64 MB na 96 MB.

Lze říct, že AMD investovala nemalé úsilí, aby nová generace procesorů nebyla limitována datovou propustností a latencemi pamětí DDR5 a výkon mohl růst bez ohledu na jejich možnosti. Vypadá to však, že jeden prvek, který má potenciál pozitivně ovlivnit paměťový subsystém, byl dosud přehlížen.

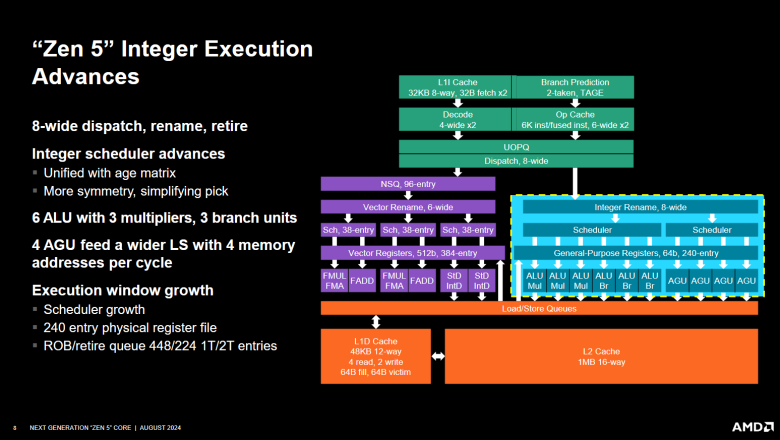

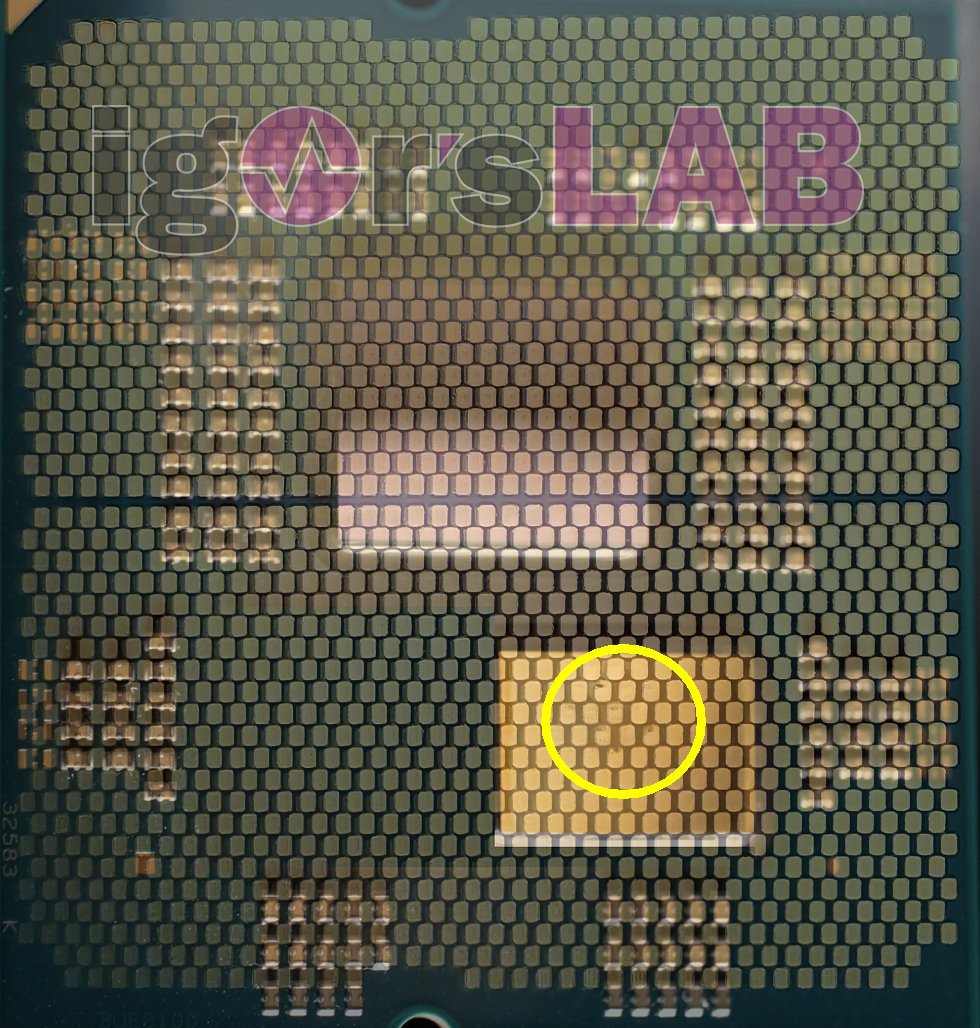

Uživatel InstLatX64 upozornil, že podle dokumentů AMD ponese jádro Zen 6 celkem 6 INT (celočíselných) schedulerů, zatímco Zen 5 měl jeden centrální. Hned zde je potřeba upozornit, že alespoň podle oficiálního diagramu od AMD měl Zen 5 dva INT schedulery. Ani to však nic nemění na skutečnosti, že navýšení jejich počtu na šest by byl velmi výrazný posun.

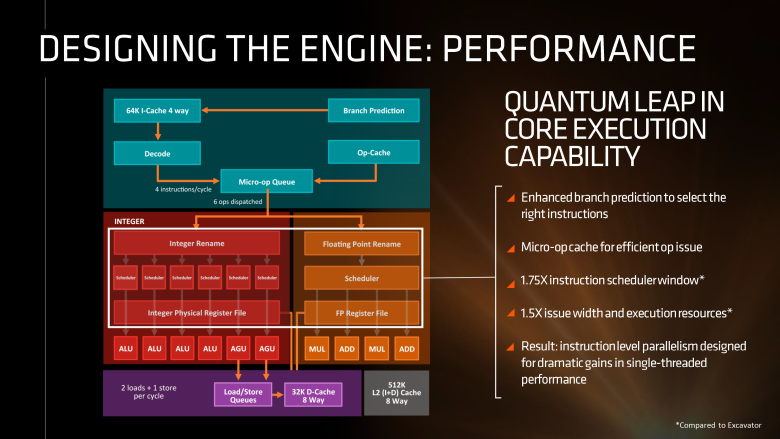

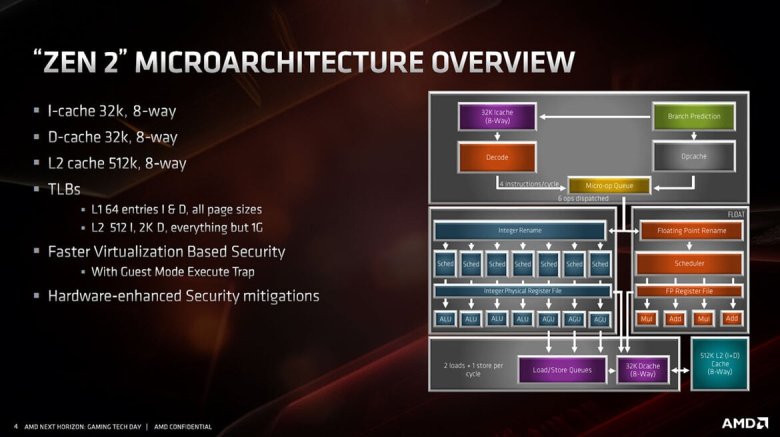

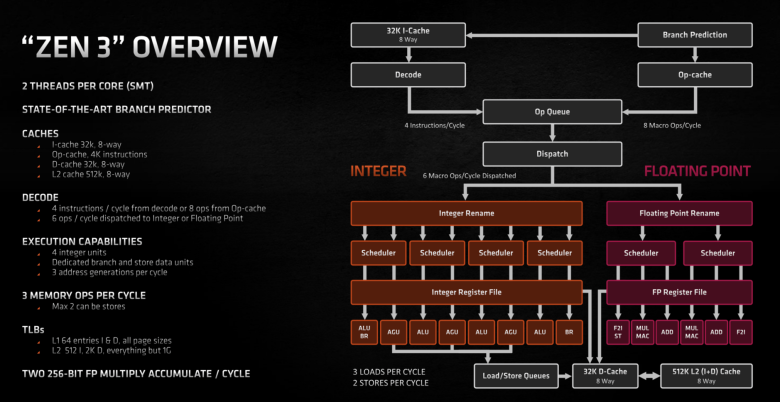

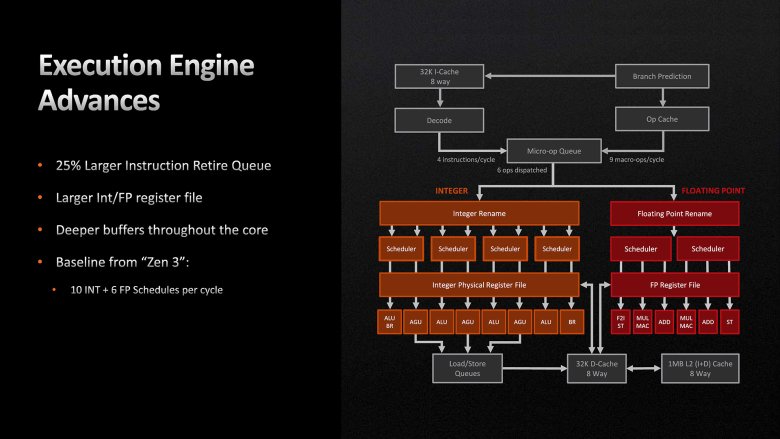

Diagramy architektur Zen (1) až Zen 4 (AMD)

Diagram architektury Zen 5 (AMD)

Připomeňme, že (alespoň podle oficiálních diagramů) měl původní Zen šest INT schedulerů, Zen 2 navýšil na sedm, Zen 3 a Zen 4 disponovaly každý třemi a Zen 5 byl vybaven dvěma.

Cílem zvýšení počtu INT schedulerů na šest je jistě vyšší efektivita při celočíselných operacích, ale nemusí jít jen o výpočty jako takové. Změna totiž může mít pozitivní dopad i na paměťově náročné operace. Výpočet adresy se u současných architektur provádí v INT pipeline (přes AGU – Address Generation Unit), protože adresy jsou celé hodnoty a pracují s celočíselnou aritmetikou. Instrukce typu LOAD/STORE se v mikro-operacích rozkládají na výpočet adresy (INT/AGU cesta), samotný load/store do L1/L2/L3 cache a případný zápis výsledku. Pokud je INT pipeline vytížená, může se stát úzkým hrdlem a může zbrzdit i část pipeline potřebnou pro paměťové operace. V takové situaci popsaná změna pomůže k dalšímu zefektivnění paměťového subsystému. Že ji AMD zařadila právě na Zen 6, který řeší právě různá úzká hrdla paměťového subsystému (jinými slovy, v důsledku odstranění řady úzkých hrdel by INT pipeline mohla být častěji limitujícím prvkem), tak nevypadá na pouhou náhodu, ale jako další prvek z poměrně komplexního řešení.