AMD plánuje 32jádrové HPC APU: Exascale Heterogeneous Processor

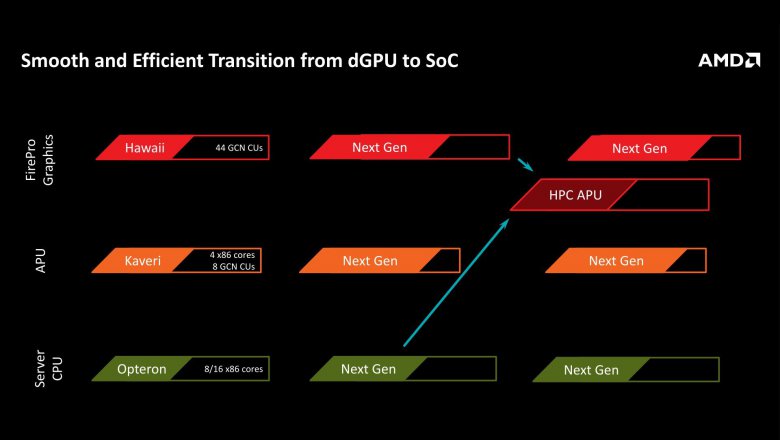

Zažíváte-li pocit déjà vu, pak se vám možná vybavily roadmapy AMD, které proběhly internetem letos v březnu. Zmiňovaly totiž existenci „HPC APU“, tedy integrovaného čipu pro výpočetní segment, který měl být postaven na příští generaci procesorové architektury s grafickými jádry příští generace FirePro.

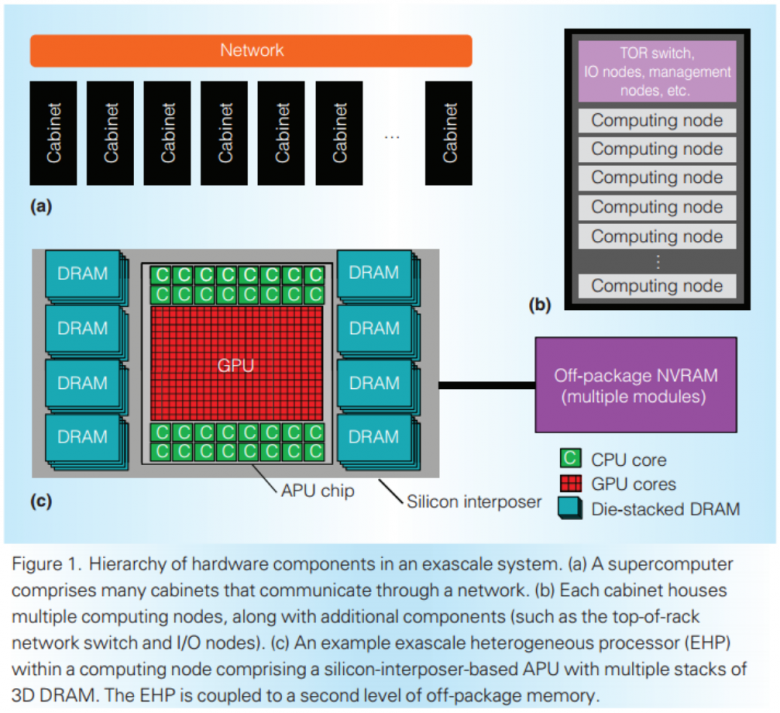

Dokument pro IEEE odhaluje něco podobného (možná totožného), ale podrobněji. Schéma znázorňuje křemíkový interposer (podložku) s výpočetním APU, které se skládá z 32 procesorových jader (C) a jádra grafického, které by mělo zaujímat významnou část plochy APU (na nákresu přes 50 % plochy). K tomu jsou připojené paměti. Není vysloveně specifikován typ, pouze koncept: „die-stacked DRAM“ resp. „3D DRAM“.

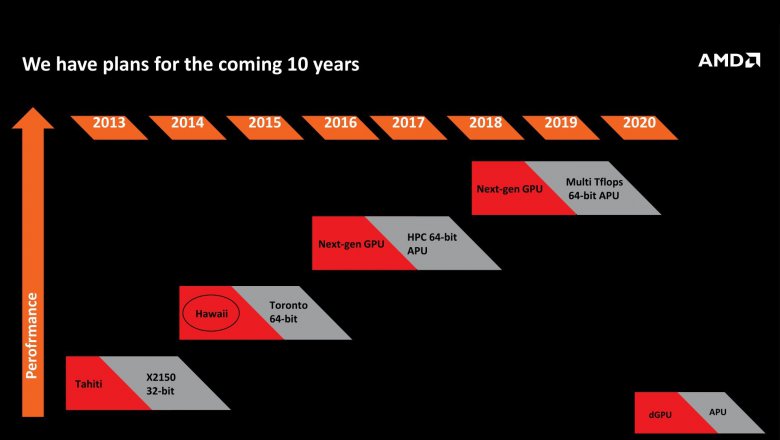

Tolik k informacím, které jsou dané. Druhá věc jsou zprávy, které na základě tohoto slajdu vznikly. Mnohé weby (Bits'n'Chips, WCCFTech aj.) hovoří explicitně o procesorových jádrech Zen, pamětech HBM a vydání v roce 2016-2017. Ani jedna z těchto informací ale není v dokumentu výslovně uvedena, takže jde o spekulace. Reálně je ale víc možností. AMD krom Zenu vyvíjí ještě architekturu ARM K12, krom HBM pamětí existují i jiné typy 3D DRAM, v úvahu by mohly připadat např. HMC (byť lze říct, že HBM jsou o něco pravděpodobnější, protože se na jejich vývoji AMD podílela). Datum 2016-2017, patrně převzaté z výše uvedené březnové roadmapy, se může týkat jiného HPC čipu.

Pokud totiž vezmeme v potaz, že by toto EHP (= Exascale Heterogeneous Processor ≈ HPC APU) neslo 32 jader Zen a k tomu mělo integrovat relativně velké grafické jádro plus čipset a další obvody, pak si lze jen stěží představit, že by něco tak velkého mohlo vzniknout na čerstvém 14nm procesu (pokud by vůbec něco takového mohlo vzniknout na 14nm procesu jako takovém). Nabízí se proto myšlenka, zda buďto oněch 32 procesorových jader nevychází z architektury K12 (namísto očekávaného Zenu), nebo - v případě Zenu - nejde spíš o záležitost roku 2018-2019, kdy bude k dispozici 10nm proces, který přinese výraznější procentuelní zmenšení (čipů) než 14/16nm oproti 20nm.