AMD si patentovala způsob implementace kombinace velkých a malých jader

Koncept ARM big.LITTLE vznikl jako řešení (jedno z možných řešení) problematiky mobilního světa. Aby úlohy běžící na pozadí (operačního systému telefonu) nevysávaly příliš rychle baterii, byla k výkonným mobilním jádrům doplněna ještě méně výkonná úsporná. Úloha na pozadí tak nemusela běžet na velkém jádru, které rychleji vysávalo baterii a telefon mohl nabídnout vyšší výdrž běhu na baterii a zároveň vyšší výkon nejnovější ARM architektury.

Tato původní verze konceptu big.LITTLE ovšem nemá v desktopu místo. Uživatel stolního počítače neocení, pokud mu spotřeba v klidu klesne z 35 wattů na 34,9 wattu a většina redakcí ani není vybavena, aby rozdíl na úrovni desetin wattu spolehlivě změřila. Zatímco v mobilu jde v důsledku omezené kapacity baterie o podstatný aspekt, který může o hodiny prodloužit výdrž na jedno nabití, v desktopu by takové řešení pouze navýšilo cenu (malá jádra nějaký křemík stojí a výtěžnost není na ploše čipu závislá lineárně, ale exponenciálně) bez hmatatelného přínosu.

Přesto může mít podobný koncept v desktopu smysl. Především tam, kde jde o procesory s vyšším počtem jader. Zatímco při jednojádrové zátěži je vytížené procesorové jádro prakticky neomezeno limitem spotřeby a může běžet, jak chce, protože na TDP limit nenarazí, čím více jader je aktivních, tím více jsou omezována. To není špatné z energetického hlediska - pokud jádra běží ne nižších taktech, jsou blíže svému energetickému optimu a poměr spotřeba / výkon je lepší.

Nemusí to ale být optimální z hlediska výrobních nákladů. Pokud navrhnu procesorové jádro, které mě stojí včetně příslušné cache 8 milimetrů čtverečních křemíku a které dosahuje výkonu (označme ho) 100 %, pak zkrátka při osazení a vytížení 16 těchto jader, která mě stála 128 milimetrů čtverečních křemíků, nebudu mít kvůli energetickému omezení výkon 16× vyšší, tedy 1600 %, ale jen např. 1100 %. Jednotlivá jádra kvůli energetickému omezení „jedou jen na tři válce“.

V takové situaci se nabízí otázka, jaký smysl má osazovat 8 mm² velká jádra, která v důsledku energetického limitu nebudou nikdy využitá na 100 %, ale třeba na 70 %, když by stejnou práci mohla odvést úspornější 4 mm² velká jádra, která by v daných energetických limitech oněch 70 % výkonu velkých jader odvedla také, plochu procesoru by klesla na 96 milimetrů čtverečních a tím i výrobní náklady a možná prodejní cena. Jak bylo řečeno, závislost výtěžnosti na ploše není lineární, ale exponenciální, takže o třetinu větší plocha 128mm² řešení (oproti 96mm²) neznamená o třetinu vyšší cenu, ale třeba o 50-60 % vyšší výrobní náklady.

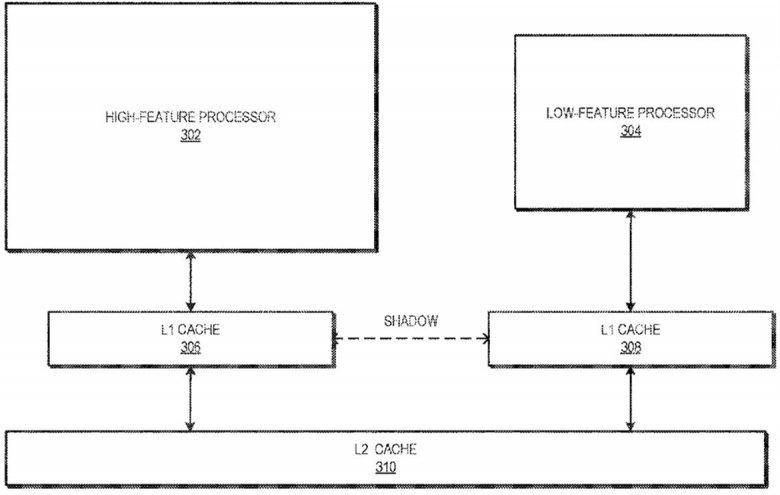

AMD se pro úsporu nákladů s architekturou Zen vydala jinou cestou. Modulární, čipletovou. Procesor rozsekala na menší kousky, čímž se na křivce exponenciální závislosti dostala výrazně níž. Intel musel reagovat a vypadá to, že zvolil právě strategii kombinace malých a velkých jader. Nyní se objevil patent, ve kterém AMD popisuje konkrétní způsob implementace tohoto řešení.

Zdá se, že si chce nechat otevřenou cestu pro případ, že by v budoucnu v tomto řešení viděla smysl. Jak ale bývá obvyklé, většina papírových technologií nikdy nenajde uplatnění a mnohé patenty zůstávají jen na papíře. Ne vše, co vypadá elegantně jako koncept, lze i snadno elegantně implementovat. Intel s mobilním procesorem Lakefield ukázal, že i firma s gigantickými finančními a personálním prostředky má jisté problémy přenést myšlenku z papíru do reálného světa. Výhody konceptu byly totiž z nezanedbatelné části setřeny kompromisy, ke kterým společnost musela přistoupit.

Prvním kompromisem bylo vypnutí HT u velkého jádra. HT je prvek, který z daného hardwaru dokáže extrahovat vyšší výkon (oproti situaci, kdy není přítomno). Nabízí se otázka, jaký smysl má implementovat řešení spořící křemík, když je integrováno na úkor technologie, která zvyšuje efektivitu využití přítomného křemíku. Druhý kompromis vyplývá z faktu, že velká a malá jádra Intelu nedisponují totožným instrukčním setem, takže - mají-li fungovat zároveň - musí dojít k deaktivaci pokročilých instrukčních setů velkého jádra (AVX, AVX2 a AVX-512) a degradaci jeho výbavy na úroveň malých jader. Opět jde tedy o implementaci technologie zvyšující poměr výkon na tranzistor za cenu vypnutí jiné technologie zvyšující poměr výkon na tranzistor.

S desktopovou generací Alder Lake již Intel použije pokročilejší architekturu malých jader, která podle dostupných informací podporuje AVX a AVX2, takže velká jádra budou v důsledku spolupráce s malými ochuzena „pouze“ o AVX-512, TSX-NI a FP16.

Pokud se AMD vážně zabývá myšlenkou kombinace velkých a malých jader, nezbývá než doufat, že počítá i s řešením těchto slabin, které jsou zatím docela podstatnými vadami na kráse tohoto řešení. Pokud nicméně vezmeme v potaz, že například takový 64jádrový Threadripper PRO 3995WX vykazuje rozdíl mezi základním taktem a boostem 2,7 / 4,2 GHz a základ je tedy 64 % maxima, pak by náhrada poloviny jader menšími a úspornějšími, které cca 2/3 výkonu jednoho velkého jádra dosáhnout také, dávala smysl a umožňovala navyšování počtu jader i při současném zpomalujícím vývoji na poli výrobních procesů.