Centrální čiplet Epyc Rome je 14nm, ale Ryzeny mají 12nm

Při ohlášení nové generace serverových procesů Epyc postavených na architektuře Zen 2 se AMD podařilo překvapit nejen tím, že jde o procesor složený z čipletů, ale do jisté míry i faktem, že centrální čiplet je vyrobený na 14nm procesu. Nebylo jasné, proč AMD nepoužila 12nm, který by mohl být mírně energeticky úspornější nebo s použitím vhodných knihoven mírně menší.

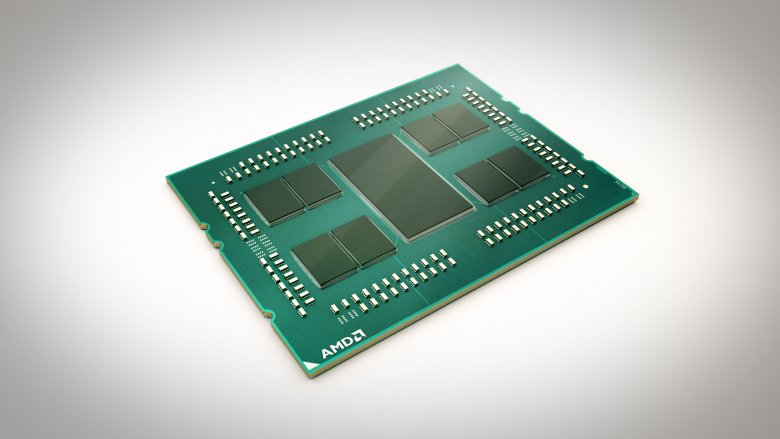

Epyc Rome se 14nm centrálním čipletem (vlevo), Ryzen 3000 se 12nm centrálním čipletem (vpravo)

Naopak na E3 společnost prozradila, že centrální čiplet na nových Ryzenech 3000 vyrábí 12nm procesem. Proč používá u serverového modelu jeden proces a u desktopového jiný? Můžeme předpokládat, že oba pocházejí od GlobalFoundries a AMD jejich odběry plní nasmlouvané odběry křemíku. Společnosti mají uzavřenou smlouvu, která zavazuje GlobalFoundries dodávat AMD křemík za exkluzivní ceny a na druhé straně zavazuje AMD k minimálnímu objemu odběrů, při kterém může GlobalFoundries tyto ceny zaručit. Pokud by AMD minimálního objemu odběrů nedosáhla, musí platit GlobalFoundries pokutu.

GlobalFoundries ale bude nejspíš docela jedno, jestli si svůj závazek AMD vyplní na odběru 12nm nebo 14nm waferů - rozdíl v procesu je minimální. Vypadá to, že důvod použití různých procesů bude tedy jinde. Jediné další možné a zároveň smysluplné vysvětlení souvisí s již dříve vyslovenou hypotézou, že výběr procesu může souviset s cache:

| 14HP is the industry’s only technology to integrate a three-dimensional FinFET transistor architecture on a silicon-on-insulator (SOI) substrate. Featuring a 17-layer metal stack and more than eight billion transistors per chip, the technology leverages embedded DRAM and other innovative features to deliver higher performance, reduced energy, and better area scaling over previous generations to address a wide range of deep computing workloads. |

Oficiální popis 14nm procesu GlobalFoundries totiž uvádí podporu pro embedded DRAM, zatímco popis 12nm procesu tuto pasáž neobsahuje. Protože se od ohlášení Epyců Rome spekuluje o tom, že jejich centrální čip bude vybaven nějakou formou LLC (last-level cache), patrně by tedy šlo o L4 cache, vysvětlovalo by to potřebu právě 14nm procesu. Oproti centrálnímu čipu desktopových Ryzenů, které L4 nemají, 14nm proces nepotřebují a jsou vyráběné na o pár procent lepším 12nm. Rozdílný proces tedy nahrává předpokladu, že nový Epyc bude vybaven L4 cache. Ta vy mohla dosahovat kapacity řekněme několik stovek megabajtů.