Epyc Rome dual-socket nabídne až 162 PCIe 4.0 linek o 315 GB/s

Redakce webu STH, který se specializuje na servery a pracovní stanice, věnovala několik měsíců přípravě analýzy poukazující, že druhá generace Epyců přináší velký posun co do konektivity. Navíc navzdory tomu, že platforma nedisponuje čipsetem (jako serverové systémy Intelu), ale „jen“ integrovaným řešením v CPU.

Vše vychází ze systému Infinity Fabric (IF), který slouží nejen jako interní sběrnice v jednotlivých čipletech a také jako externí sběrnice k propojení čipletů, ale navíc i ke vzájemnému propojení čipů v oddělených socketech. IF spojující sockety je implementována jako jednotné rozhraní, které může být využito buďto jako blok PCIe ×16 (zde 4.0), nebo použít protokol Infinity Fabric, ve kterém jsou datové přenosy zhruba 2× rychlejší. Stejně jako byla mezigeneračně zdvojena přenosová rychlost PCIe (3.0->4.0), tak byla zdvojena i přenosová rychlost nové generace IF.

U stávající generace (či minulé, záleží, jak na to nahlížíte) Epyců spojovaly sockety čtyři linky IF, což znamená, že na komunikaci mezi oběma procesory bylo vyčerpáno 8 bloků PCIe ×16 (čtyři na každém procesoru). Nadcházející Rome rovněž realizuje spojení čtyřmi PCIe ×16 bloky na každém procesoru (tj. osmi celkem), ale je flexibilnější. Vychází z faktu, že s těmito čtyřmi linky je díky 2× rychlejší Infinity Fabric rychlost spojení obou procesorů 2× vyšší, což nemusí být vždy nutné. Pokud tedy jde o systém (desku) určenou pro server, kde jsou těžištěm PCIe akcelerátory (GPU, FPGA…) nebo velké množství úložišť vyžadující velké množství řadičů připojených na PCIe a kde tedy x86 procesor slouží spíše jako obsluha těchto rozhraní, pak je možné snížit počet IF linek mezi procesory na 3. Tím se na každém procesoru uvolní 16 PCIe linek, celkem tedy k volnému použití přibude 32 PCIe 4.0.

Právě tato konfigurace je znázorněna na úvodním schematu. Každý procesor je vybaven osmi bloky PCIe ×16, tři na každém jsou využité jako IF, tzn. na každém procesoru zbývá pět bloků PCIe ×16, tzn. 10 bloků celkem. To dává 10 ×16 = 160 PCIe 4.0 linek pro celý systém.

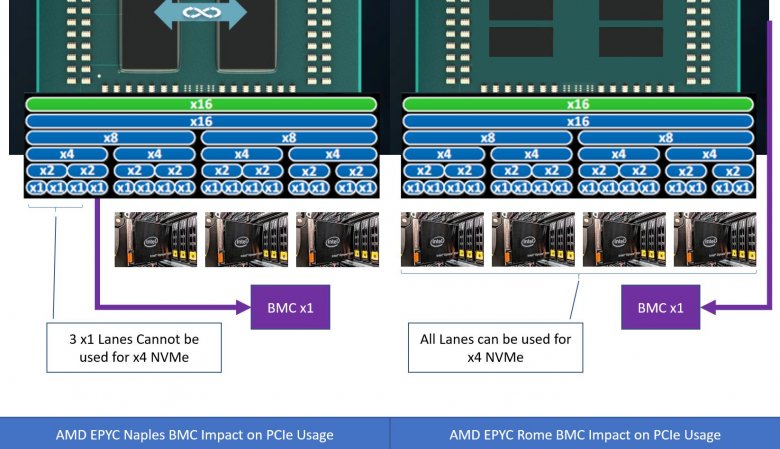

BMC link

To však není vše, protože AMD Epyc Rome ještě mírně vylepšila. Původní Epyc teoreticky disponoval celkem 128 PCIe linkami (osmi bloky ×16), ale jejich využití bylo v jednom ohledu problematické - žádná běžná deska nenabídla těchto 128 linek v PCIe slotech. Důvodem je BMC neboli Baseboard Management Controller. V praxi jde o řídící čip osazený na většině serverových desek, který je pro účely komunikace s procesorem vybaven PCIe ×1 linkou.

Právě tato jedna linka znamenala, že byl z hlediska využitelnosti v socketu vyřazen jeden PCIe ×16 blok, kam byla tato linka připojena. Bylo samozřejmě možné zbývajících 15 linek rozdělit mezi nějaké řadiče na desce, ale ty nemusely být vždy žádané - navíc po vyčerpání tří zbývajících ×4 zůstala ještě jedna ×2 a jedna ×1 linka, kde možností využití příliš nebylo. Epyc Rome proto na úroveň procesoru doplní jednu bonusovou PCIe ×1 linku navíc, takže i po osazení BMC zůstane procesoru krásných kulatých 128 PCIe linek (plných osm bloků ×16).

Toto řešení se zdá být dokonce elegantnější než přístup Intelu, který BMC připojuje k lince vyvedené z externího čipsetu. Tím sice ochrání „celistvost násobků“, ale na připojení externího čipsetu spotřebuje část linek, jimiž je vybaven procesor.

Epyc Rome tedy bude procesor vybaven celkem 129 PCI linkami (254 GB/s). V případě dvousocketové konfigurace pak podle potřeby systému (což bude dáno deskou) je možné využít konfiguraci se:

- 4 IF linky + 128 PCIe 4.0 (celkem 130 včetně dvou „×1“), tj. 256 GB/s

- 3 IF linky + 160 PCIe 4.0 (celkem 162 včetně dvou „×1“), tj. 319 GB/s

Teoreticky by byla možná i konfigurace, která staví na dvou linkách IF (tzn. stejné vzájemné propustnosti jako u původního Epycu):

- 2 IF linky + 192 PCIe 4.0 (celkem 194 včetně dvou „×1“), tj. 382 GB/s

Ovšem taková prý zatím nebyla v žádné dokumentaci uvedena a žádný výrobce s ní zatím nepočítá. Berme ji proto jako spekulativní možnost, kterou by časem AMD nebo některá firma vyrábějící servery / desky mohla zpřístupnit, pokud by se objevil zákazník preferující maximální počet PCIe rozhraní. Nemusí se samozřejmě objevit vůbec, neboť i konfigurace postavená na 3 IF linkách nabídne až 10 plnotučných PCIe 4.0 ×16 slotů na základní desku.

23. dubna pořádá AMD akci pro partnery, na které jim představí 7nm novinky. Lze předpokládat, že po tomto datu dojde k úniku části odprezentovaných informací o nadcházjících procesorových i grafických produktech.