JEDEC vydal JESD235A specifikaci, rozšiřuje HBM o pseudo-channel a pojistku

Pro začátek asi bude třeba určitých upřesnění a vysvětlení. Standard vrstvených pamětí HBM s širokým rozhraním a nízkou pracovní frekvenci byl odklepnutý v říjnu 2013. Otevřeně se o nich začalo mluvit (jakožto o konkrétním produktu a jeho nasazení) koncem roku 2014. Zhruba před rokem došlo na první zmínky o HBM2, ale již tehdy se objevovaly názory, že tento název je trochu zavádějící, protože co je označováno jako HBM2, se od HBM liší jen výrobním procesem, možností vyššího počtu vrstev a spíše dílčími změnami - nikoli základní architekturou nebo funkcionalitou.

JEDEC nyní v lednu vydal (v listopadu dokončenou) specifikaci, která se jmenuje „JESD235A - High Bandwidth Memory (HBM) DRAM“. Jde o rozšíření (revizi) specifikace JESD235, původního HBM standardu z roku 2013. Nový dokument dává za pravdu kritikům marketingové (či pracovní) zkratky HBM2, protože ji vůbec nezná - nadále hovoří výlučně o HBM a dělení na HBM1 a HBM2 nedefinuje.

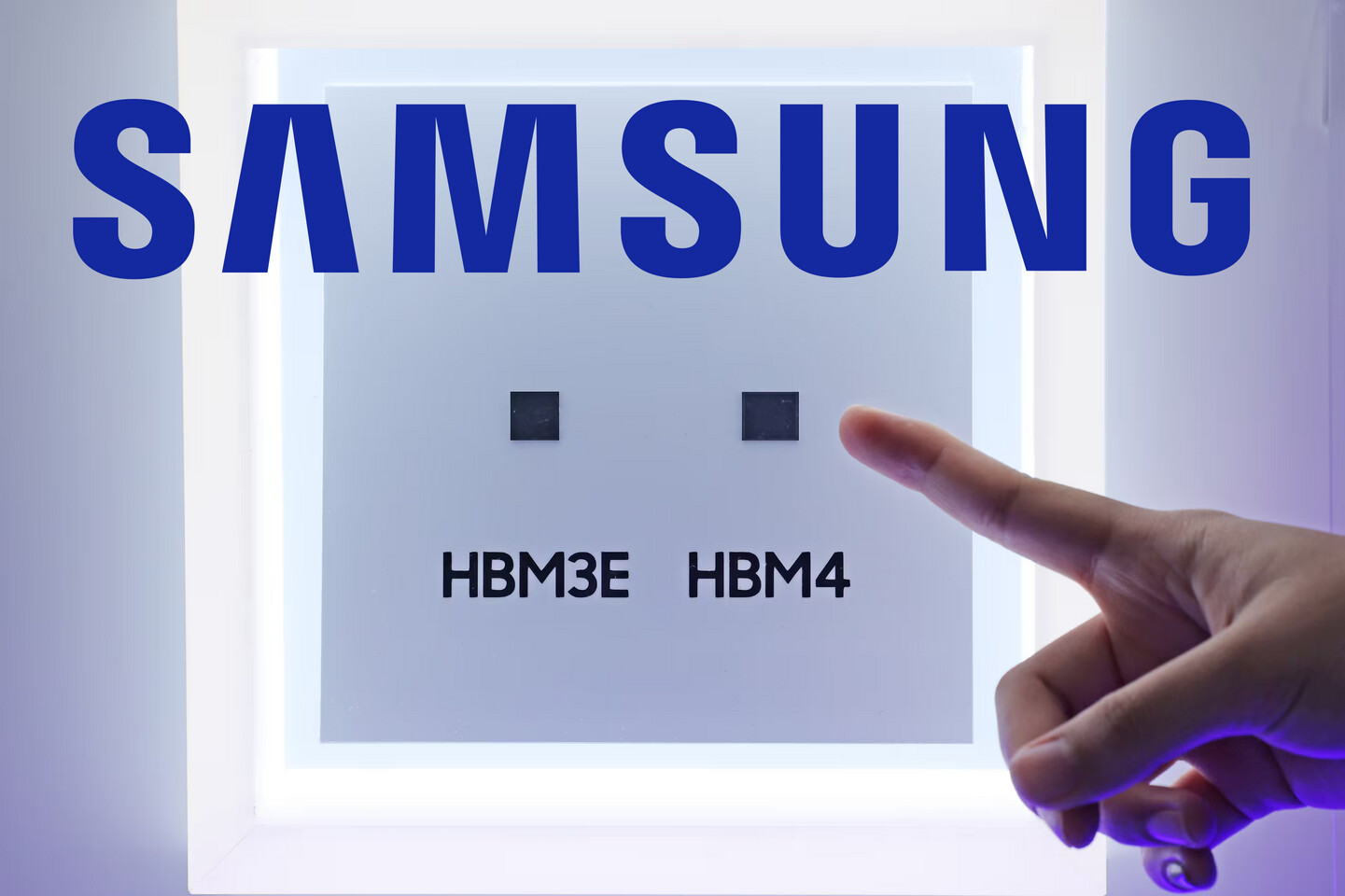

Striktní dělení na HBM1 a HBM2, které bylo dávané do souvislosti s výrobním procesem (HBM1: 29nm, HBM2: ~20nm) se s ohledem na oficiální specifikaci jeví jako bezpředmětné i v tomto ohledu: JEDEC výrobní procesy nestanovuje ani v původním a ani v aktualizovaném standardu. V tomto kontextu dává smysl vyjádření Hynixu, který už v souvislosti s 29nm generací čtyřvrstvých čipů (= ty čipy použité na Radeonech Fury) tvrdil, že v principu nic nebrání výrobě osmivrstvé varianty. Specifikace JEDEC opět dávají této možnosti zapravdu, původní standard JESD235 z roku 2013 počet vrstev na 4 neomezoval, naopak uváděl i příklad s použitím osmi vrstev (při jednom kanálu na vrstvu - očekávaný limit osmi kanálů na čip opět zůstal zachovaný i v nové specifikaci).

| výrobní proces | počet vrstev | počet kanálů | pseudo channel | teplotní varování | |

| JESD235 | nespecifikován | očekáván až 8 | až 8 | ||

| JESD235A | nespecifikován | očekáván až 8 | až 8 |

Pokud si to tedy shrneme, není výrobní proces ani počet vrstev záležitostí, kterou by určovala specifikace, ale čistě věcí aktuálních možností výrobních technologií (Hynixu, Samsungu…). Skutečný rozdíl mezi HBM1 a HBM2 (pokud přimhouříme oči nad tím, že tyto termíny JEDEC nezná) spočívá v něčem jiném. U jednotlivých čipů zůstává zachované fyzické 1024bit rozhraní, ale standard JESD235A umožňuje použít tzv. pseudokanálovou architekturu (pseudo-channel architecture) pro zvýšení efektivních datových přenosů (na dvojnásobek). Druhý rozdíl spočívá v možnosti monitoringu kritické teploty („Catastrophic Temperature Sensor“) - řídící obvody se dozví, pokud teplota čipu přesahuje bezpečnou mez.

Monitoring nebezpečné teploty funguje tím způsobem, že každá z vrstev čipu obsahuje teplotní snímač, který komunikuje s řídícím obvodem. Teplota je reportována přes 3bit rozhraní. Čip má stanovený rozsah bezpečných teplot. Ten není věcí specifikace JEDEC, ale vkládá jej výrobce čipu podle vlastního uvážení. Pokud dojde k překročení limitu „Catastrophic Temeperature“, je tento stav reportován a čip vypnut. Tato vlastnost není povinná pro všechny HBM čipy, pouze pro ty s přenosovou rychlostí nad 4 Gb/kanál a dále u 2 Gb/ kanál pro čipy využívajících pseudo-channel. V podstatě tím jsou definované čipy určené pro výkonná zařízení (grafické karty, výpočetní karty atp.), kde by k přehřátí mohlo dojít. HBM mají stanovené měření teploty už předešlou specifikací (8bit rozhraní, kde je 7 bitů vyhrazených pro údaj o konkrétní teplotě ve °C). Nový Catastrophic Temperature Sensor je tedy spíš pojistkou každé vrstvy, bezpečnostní ochranou před zničením čipu.

Výrobní proces i počet vrstev tedy definované nejsou, jde čistě o důsledek aktuálních technologických možností výrobce - v tomto případě Hynixu, od nějž prvotní informace o počtu vrstev, výrobních procesech a kapacitě čipů pocházely. Interpretace těchto parametrů jakožto součásti specifikace pamětí ale byla chybná.