Nova Lake: Výkon, 288 MB cache v procesorových dlaždicích a konfigurace

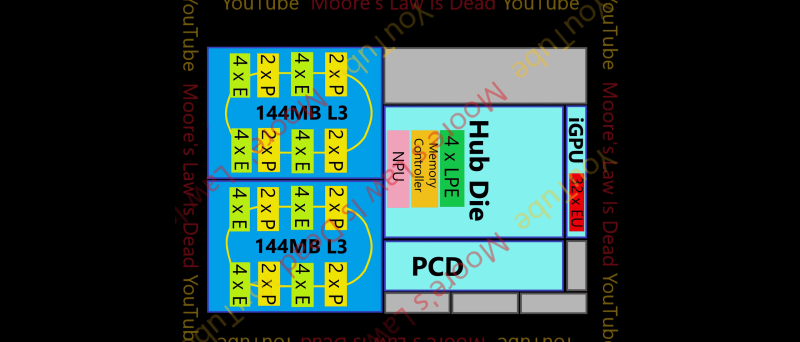

Nova Lake je příští generace procesorů Intelu chystaná na konec roku 2026 (letos pro desktop dorazí Arrow Lake-refresh s vyššími takty). O Nova Lake již víme, že bude využívat až dvě procesorové dlaždice, každou s 8 velkými a 16 malými jádry, tedy 48 jádry celkem. Další 4 (úsporná) jádra budou přítomna v centrální dlaždici. Opakovaně se mluvilo i o tzv. bLLC, tedy „big last level cache“, velké cache poslední úrovně, která má být jakousi odezvou na V-cache (X3D) od AMD.

Nově se dozvídáme, že bLLC nebude ani navrstvená (jako V-cache), ani implementovaná samostatným kouskem křemíku, ale podle MLID bude prostě monolitickou součástí procesorových dlaždic. Jinými slovy půjde o dlaždici, která nese 8 velkých jader, 16 malých jader a 144MB L3 cache. To v praxi znamená, že z hardwarového hlediska není tato cache volitelná (nelze ji prostě osadit či neosadit jako V-cache nebo další čiplet či dlaždici), ale v high-endu bude patrně přítomná vždy.

Nova Lake (MLID)

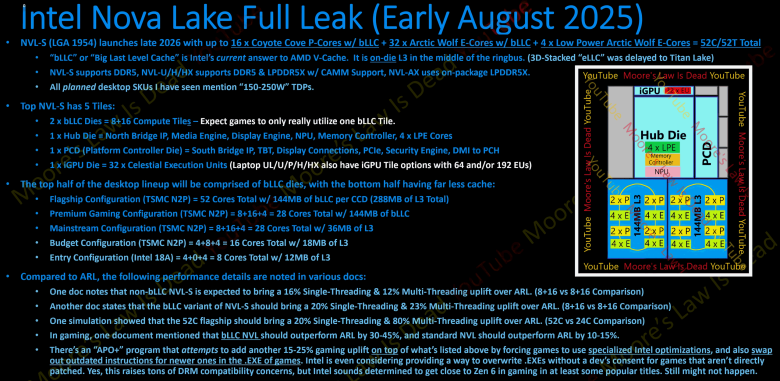

Pro mainstream, kde bude přítomna jen jedna dlaždice, Intel počítá jak s dlaždicí se 144MB L3 cache (herní varianta), tak s menší dlaždicí s 36MB L3 (standardní mainstream). Dále Intel chystá procesorovou dlaždici, která krom L3 cache (18MB) sníží i počet jader (4+8) a nakonec ještě low-endové řešení vybavené pouze 4 velkými jádry a 12MB L3 cache. To je, jako jediné z potvrzených, vyráběné u Intelu na vlastním 18A procesu. Všechny vyšší konfigurace vzniknou u TSMC na procesu N2P.

| konfig. CPU dlaždice | jádra | L3 cache | proces | výkon vs. 285K |

|---|---|---|---|---|

| top model | 2× 8+16 | 288 MB | TSMC N2P | +20 % / +80 % |

| herní model | 8+16 | 144 MB | TSMC N2P | +20 % / +23 % |

| mainstream | 8+16 | 36 MB | TSMC N2P | +16 % / +12 % |

| nižší mainstream | 4+8 | 18 MB | TSMC N2P | ? |

| low-end | 4+0 | 12 MB | Intel 18A | ? |

V praxi to znamená, že jen na výrobu desktopového Nova Lake musí Intel u TSMC objednat 3 typy dlaždic, které budou vyráběné 2nm procesem. To je podstatný rozdíl oproti přístupu AMD, která základní modely desktopového, mobilního i serverového Zen 6 postaví na jediném návrhu procesorového čipletu (12× Zen 6) a další segmentace bude řešena přítomností jednoho či více procesorových čipletů, (ne)přítomnosti V-cache, (ne)přítomnosti dalších jader v centrálním čipletu atd.

Množství různých návrhů a tudíž potřeba většího počtu masek však nebude jediným rozdílem v nákladech. Pokud Intel plánuje postavit high-end výhradně na dlaždicích vybavených bLLC, pak to znamená, že i uživatel provozující aplikace, které těží z vyššího počtu jader (ale nikoli z velké cache) nebude mít jinou možnost než koupit produkt s 288MB cache. Pro Intel to pak znamená výrazně zvětšení každé 2nm dlaždice, což je z dvou důvodů dost zásadní skutečnost. V první řadě je již delší dobu známo, že SRAM (na které je postavena L3 cache) s moderními procesy poměrně špatně škáluje, takže je z hlediska cena / kapacita výhodnější vyrábět velké cache na zvláštním křemíku starším procesem. Druhou skutečností je cena 2nm křemíku TSMC. 2nm wafer TSMC stojí $30 000, zatímco 6nm wafer téže značky vychází kolem $10 000, přičemž z funkčního hlediska pro SRAM nepředstavuje novější proces žádnou zásadní výhodu, jen je prostě násobně dražší. Z hlediska nové strategie Intelu, která má být zaměřena na marže, je takové řešení jen obtížně pochopitelné.

Pozitivnější jsou informace o výkonu oproti Arrow Lake. Jednodlaždicová konfigurace se standardní cache (tzn. základní mainstream oproti top-modelu) má přinést ~16% posun jednojádrového a ~12 % vícejádrového výkonu. Jinými slovy: Mainstreamový Nova Lake bude výkonnější než high-endový Arrow Lake. Jednodlaždicová verze s velkou cache má přinést ~20% posun jednojádrového a ~23% vícejádrového výkonu. Podle jedné(!) simulace má dvoudlaždicový Nova Lake dosáhnout o ~20 % vyššího jednojádrového a o ~80 % vícejádrového výkonu než Arrow Lake.

To jsou o něco vyšší čísla, než jaká se objevila v červnu (+10 / +60 %) a zdá se, že jsou nejspíš důsledkem vyšších taktů. Podle MLID totiž jeden z dokumentů uvádí, že TDP Nova Lake má být „150-250 wattů“, přičemž není jasné, zda půjde skutečně o TDP (s tím, že PL2 bude ještě vyšší), nebo 250 wattů má být PL2 limit.

Nova Lake nicméně začíná z výkonnostního hlediska vypadat zajímavěji. Otázkou bude cena modelů s velkou L3 cache, která by podle MLID měla vzniknout na drahém 2nm procesu a vycházet tedy výrobně dráž než řešení od AMD. Těžko říct, zda Intel bude chtít nabídnout výhodné ceny a sníží si marže, nebo bude držet vyšší marže, ale koncová cena pak bude vyšší než u konkurence.