Plány Nvidie na poli integrovaných grafik

Na chvilku se zastavíme a povíme si, jak vlastně funguje dnes integrovaná grafika v čipsetech Nvidia. Je zvykem, že integrovaná grafika používá coby frame buffer část operační paměti celého počítače. V případě dosavadních platforem Intel s paměťovým řadičem v čipsetu je to jednoduché, paměťový řadič je přímo součástí čipsetu a integrovaná grafika to má do paměti stejně blízko jako grafika samostatná, která má vlastní dedikovanou paměť. Zkrátka je to neblíže, jak to jen jde (samozřejmě za předpokladu, že paměť je ve formě samostatných čipů, ale to je dnes tak nějak normální). U procesorů AMD je to mírně komplikováno skutečností, že paměťový řadič není v čipsetu, ale v procesoru, nicméně tyto dvě komponenty spolu však komunikují skrze relativně svižný HyperTransport, takže i když je to do paměti dál, pořád se jedná o použitelně svižné (na integrovanou grafiku) řešení. I tak třeba AMD u některých čipů volí řešení lokální cache a jistě víte, že spousta integrovaných grafik ATI má včetně nejčerstvějšího čipsetu AMD 785G možnost připojit přímo k čipsetu nějaký ten paměťový čip na tzv. SidePort.

Intel však s příchodem mikroarchitektury „Nehalem“ zavádí několik specialit. Tou první je integrace paměťového řadiče přímo do procesoru podobně, jako to má AMD. Tou druhou a z hlediska možnosti tvorby čipsetů zásadní, je nové komunikační rozhraní. A protože to není jen o „spojení jednoho čipu s druhým přes nějaké ty vodiče“, ale především o licenci na použití patřičného komunikačního rozhraní a příslušného protokolu, nemůže Nvidia jen tak přijít s vlastním čipsetem s integrovanou grafikou. A aby to bylo komplikovanější, nové procesory Core i7, i5 a i3 už nemají integrovaný jen paměťový řadič, ale prakticky celý severní můstek a v modelech, které počítají s integrovanou grafikou, i tu grafiku. Je tedy logické, že přidání dalšího čipsetu s integrovanou grafikou je poněkud mimo mísu, když už se s integrovanou grafikou počítá i v procesorech.

Pochopitelně ne všechny procesory budou tu integrovanou grafiku mít a pak je možné použít grafiku jinou. Jako nejsnazší řešení se jeví být grafika pro PCI Express ×16 rozhraní. Nvidia hodlá nadále tvořit čipsety i pro tyto nové procesory a dokonce v nich chce mít i tu integrovanou grafiku. Ač to tedy zní tak trochu jako kacířská myšlenka, Nvidia skutečně chystá „jižní můstek s integrovanou grafikou“. A vůbec jí nevadí, že takový jižní můstek bude s procesorem komunikovat skrze DMI (čipset, který počítá s integrovanou grafikou v procesoru, je s procesorem propojen také pomocí FDI, aby byl zajištěn grafický výstup), což je spoj realizovaný přes čtyři vyhrazené pro operační systém transparentní PCI Express linky.

Když si uvědomíte, že celá grafika i s vlastní pamětí se do počítače obvykle strká přes PCI Express ×16 slot, zdá se být PCI Express ×4 rozhraní v čipu, který musí také obsluhovat SATA řadiče, USB, PCI a další drobnosti, poměrně úzké. A protože na to Nvidia myslí (a teď přichází další tak trochu kacířská myšlenka), bude mít tento „jižní můstek s integrovanou grafikou“ také vlastní paměťový řadič. Jeho 64bitové rozhraní bude určeno pro připojení lokální paměti pro integrovanou grafiku. Docela jsme nepochopili, zda půjde jen o podobnou lokální cache, jako mají čipsety AMD s integrovanými Radeony, nebo bude mít integrovaná grafika celý frame buffer navěšený na sobě a nebude si nic brát z RAM, přičemž ale to druhé řešení se zdá být pravděpodobnější. Asi bychom potom takový čip neměli vzhledem ke konstrukci nazývat „jižní můstek s integrovanou grafikou“, ale naopak „grafika s integrovaným jižním můstkem“.

Pokud jde o licenci na DMI, zatím stále nevíme spolehlivě, zda ji Nvidia má či nikoli. Kdyby šlo jen o to PCI Express rozhraní, asi opravdu není co řešit, ale DMI je mimo jiné i protokol, podle něhož spolu na tom PCI Express ×4 rozhraní čipy komunikují. Na to nejspíše licence potřeba bude. Právě jsme dohovořili o čipu MCP99, který by se měl objevit na trhu v prvním kvartálu za předpokladu, že Nvidia licenci má nebo ji získá a že všechno půjde podle plánu.

Pokud jde o MCP89, to má být nástupce platformy ION stále ještě komunikující s procesory skrze FSB (interně víme, že by měl umět komunikovat i s procesory VIA skrze V4 bus, což je něco velice podobného, vlastně to není „stejné“ především z licenčních důvodů). Jestliže tedy MCP79 (nebo MCP7A) nazýváme ION, MCP89 bude ION 2. Předpokládá se, že o tento čip bude mít zájem Apple (protože dosavadní ION pod názvem GeForce 9400 obsahuje MacBook Pro) a že bude uveden ještě před koncem tohoto roku.

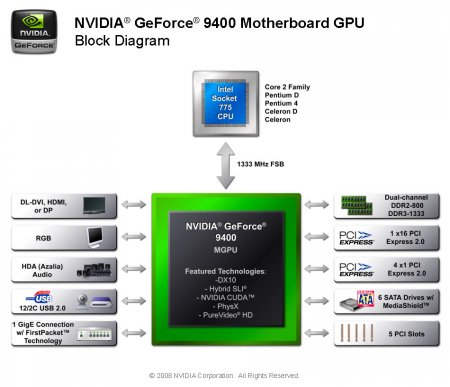

A konečně MCP85, kolem nějž panují trošku nejasnosti. To má být čipset pro procesory AMD, ale HKEPC píše, že bude pro Intely s podporou až 1 333MHz FSB a pamětí DDR3-1333, nicméně DigiTimes nyní píše, že má jít o čipset pro AMD notebooky, takže zatím zůstaneme u toho, že to prostě bude pro procesory AMD. Plánovaná doba uvedení je opět hrubým nástřelem a ten zní první čtvrtletí příštího roku.