Ryzeny 9000X3D vydá AMD v říjnu i v lednu

Prakticky od jara přicházejí zprávy o době vydání Ryzen 9000X3D i o tom, že se Zen 5 se může na X3D modelech něco změnit, zkrátka že by v nějakém ohledu mohly být uživatelsky zajímavější než Ryzen 5000X3D a Ryzen 7000X3D.

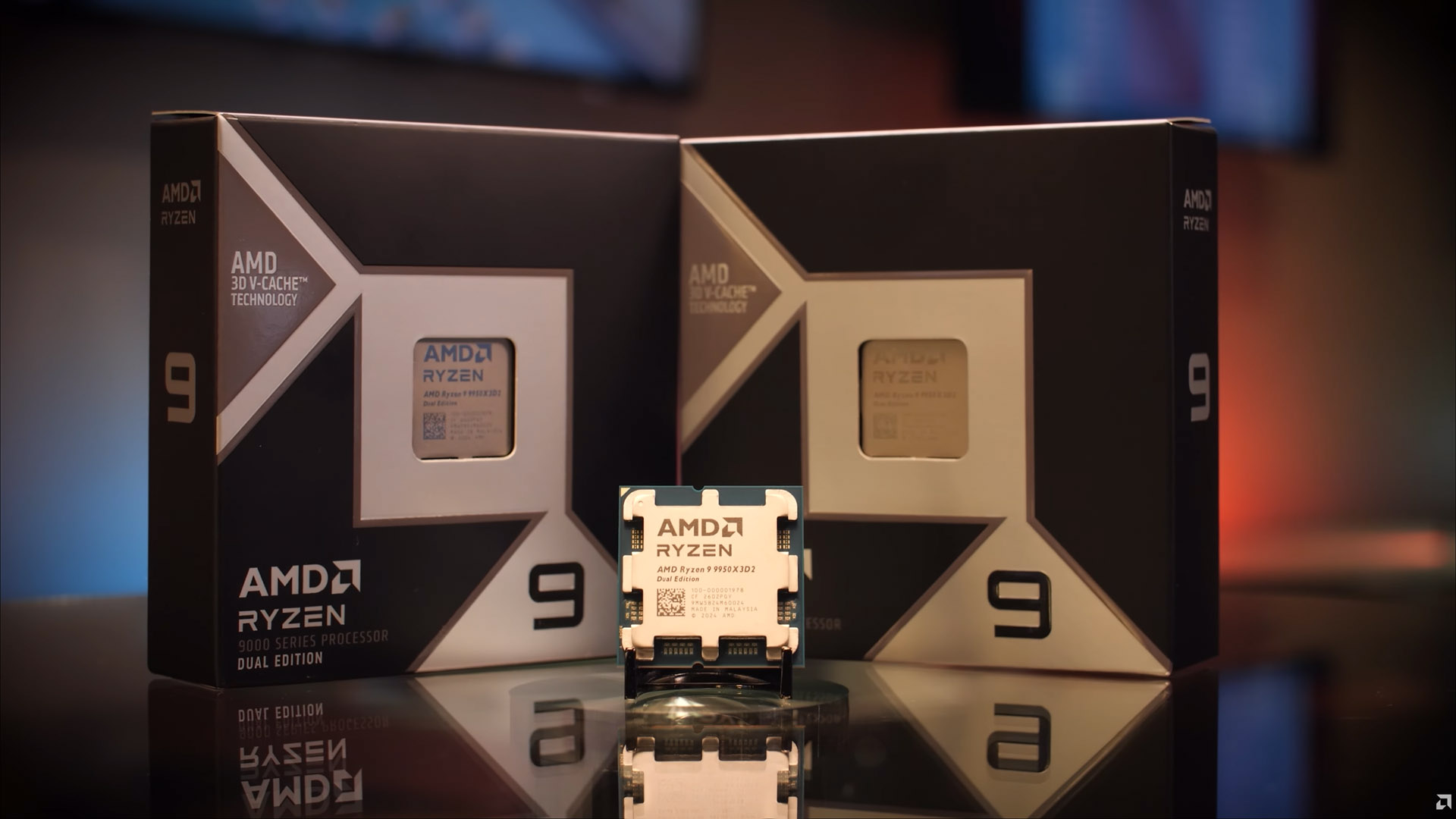

Pokud jde o datum vydání, mluvilo se střídavě o lednu (CES 2025) a o říjnu (reakce na desktopové procesory Arrow Lake od Intelu). Různé zdroje uváděly různé možnosti a poměrně zásadně si za nimi stály. Nyní se od leakera zhangzhonghao z diskuzního fóra webu ChipHell dozvídáme, že na akci společnosti Gigabyte k příležitosti vydání desek s čipsetem X870, kde kromě jejích zaměstnanců vystoupili i pracovníci AMD, se situace vyjasnila. Mělo dojít na celkem jasný náznak toho, že osmijádrový Ryzen 7 9800X3D bude vydán letos v říjnu jako reakce na Arrow Lake, zatímco vícečipletové (dvanáctijádrové a šestnáctijádrové) modely Ryzen 9 9900X3D a Ryzen 9 9950X3D dorazí příští rok. Důvodem je, že právě modely s více čiplety budou vybaveny onou technologickou novinkou.

Spekulace

Právě skutečnost, že modely se dvěma CCD (procesorové čiplety) se budou lišit od modelu s jedním CCD, by byla v souladu s naší červnovou spekulací, která vznikla jako reakce na oficiální oznámení toho, že X3D pro Zen 5 bude „zajímavá, odlišná a vylepšená“.

| Jako další možnost mne napadá umístění procesorových čipletů na křemíkovou podložku [interposer], která by SRAM integrovala. Tam by nebylo potřeba vyvíjet nové čiplety (čiplety vybavené rozhraním pro křemíkovou podložku AMD chystá pro APU Strix Halo, které se právě na začátek roku 2025 chystá a které právě s integrací cache poslední úrovně počítá), ale navýšilo by to náklady o cenu podložky. Výhody by ale byly zřejmé: (1) Žádná degradace taktovacích frekvencí, (2) cache dostupná pro oba procesorové čiplety, (3) oproti cache na centrálním čipletu podstatně rychlejší rozhraní mezi CPU jádry a cache poslední úrovně). Jde de facto o řešení, které se v desktopu očekávalo až se Zen 6, takže je otázkou, zda jej AMD bude chtít využít takto (řekněme) s předstihem. Zajímavé, odlišné a vylepšené by to však bylo bezpochyby. |

Zatímco pro řešení s jedním CCD by křemíková podložka mohla procesor zbytečně prodražovat, u dvojice CCD (Ryzen 9) by se snáz rozpustila v celkové ceně produktu a navíc by mu přinášela unikátní výhody. Větší cache by totiž v takovém případě byla dostupná oběma CCD, nikoli jen jednomu, takže by z ní mohly profitovat i aplikační zátěže náročné na datové přenosy nebo latence. Zároveň by takové řešení přineslo výraznější segmentaci - Ryzen 9 X3D by se od Ryzen 7 X3D nelišil jen počtem jader, ale i podporou vyšších taktů (i herní výkon by mohl být vyšší).

Zda se do takto odvážného řešení AMD pustí již se Zen 5, je zatím otázkou. Technologicky by to mělo být začátkem roku 2025 vyřešené, protože cosi podobného se chystá u čipletového APU Strix Halo. Spíše než o otázku technickou jde tedy o rozhodnutí strategické - tedy zda něco takového pustit na trh dříve než s generací Zen 6. Právě ta měla být podle starších zpráv první, která by takové řešení nabídla.