Samsung představil 3D balící technologii pro paměťové čipy

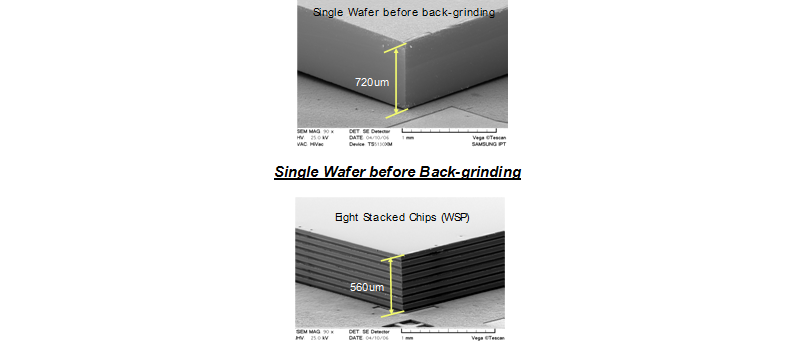

Napojení jednotlivých čipů realizuje svislými „vodiči“ jdoucími skrze čipy ležící mezi připojovaným čipem a PCB. Do těchto čipů se prostě laserem „vyrazí“ průchozí (mikroskopické) dírky, které se následně vyplní vodivým materiálem. Řada takto navrstvených vodivě vyplněných děr následně tvoří svislý přípojný vodič mezi vrchním čipem a PCB. Na obrázku pak vidíte i jakou úsporu místa to přináší, WSP prototyp v sobě nese osm čipů o tloušťce 50 µm.

Oproti stávajícím vícevrstvým čipům typu 16Gbitových NAND flash, které mají připojení k PCB realizováno ještě „konvenčním“ způsobem, přináší dle Samsungu WSP úsporu až 30 % v tloušťce čipu a až 15 % ve zbývajících dvou rozměrech. WSP metoda pak stojí i za úsporou nákladů při výrobě, kdy odpadají některé výrobní kroky, nově nahrazené pouze „vrtáním děr“ laserem. Stejně tak, což jistě řadu z vás napadlo, díky svislým přímým propojkám se zkracuje délka vodičů mezi čipem a PCB, což umožňuje navýšení frekvence bez zvýšení rizika vzájemného ovlivňování signálových cest.

Ideálním odbytištěm je segment přenosných zařízení typu PDA či mobilních telefonů, kde se mimo jiné klade důraz i na co největší kapacitu při co nejmenších rozměrech. Flash paměti (a tudíž i desktopové/notebookové Solid State disky) jsou dalšími vhodnými adepty pro nasazení takovýchto čipů. Jejich rychlosti totiž nejsou nikterak závratné. Myslíme tím třeba ve srovnání s GDDR3 pamětmi, tepajícími na 900 MHz, efektivně 1 800 MHz a přenášejícími řádově mnohonásobně více dat. U těch by totiž při nějakém masivním vrstvení čipů na sebe již nastával fatální problém s odvodem vznikajícího tepla, což u Flash nehrozí.

A kdy se toho dočkáme? Samsung plánuje rozjet výrobu NAND pamětí WSP metodou počátkem příštího roku. Později se k tomu přidají modifikace v zapouzdření těchto vícevrstvých čipů, kdy by mělo dojít i k nasazení této technologie ve výrobě paměťových čipů pro serverové nasazení.