Skládání procesorů z křemíkových modulů snižuje AMD náklady o ~40 %

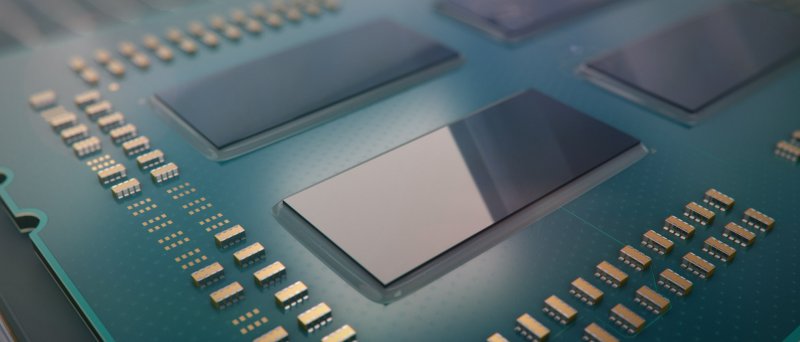

Jedno křemíkové osmijádro (Zeppelin) dosahuje plochy 213 mm². Pokud AMD vyrábí šestnáctijádrový procesor, použije dvě (tj. celkem 426 mm² křemíku), pokud vyrábí dvaatřicetijádrový procesor, konkrétně serverový Epyc, použije čtyři, tedy celkem 852 mm² křemíku.

Jak velký by takový 32jádrový procesor byl, pokud by byl vyrobený jako monolit, vyčísluje AMD ve slajdu níže. Obvody, které by v případě monolitu bylo možné vynechat (rozhraní externí Infinity Fabric a duplicitní obvody) měří v případě každého křemíkového (osmi)jádra 18,75 mm², což znamená, že v případě 32jádrového monolitu by stačila celková plocha 777 mm² (namísto stávajících 852 mm²).

Jenže druhá strana mince, tentokrát ale významnější, je výtěžnost. Ta s plochou jádra klesá exponenciálně, jinými slovy náklady na výrobu s plochou stoupají exponenciálně. 75 mm² křemíku navíc u skládaného řešení tak zvyšuje výrobní náklady výrazně méně, než výroba hypotetického monolitu. Podle AMD jsou celkové náklady na skládané 32jádrové CPU o 41 % nižší, než by byly u monolitu.

Zkrátka, pokud se na ploše ~800 mm² objeví jeden defekt, tak v případě monolitu to v lepším případě znamená, že bude nutné vypnout dvě jádra (pokud defekt vyjde na jádro nebo příslušnou část cache), v horším případě, že jádro půjde na recyklaci (pokud se defekt trefí do obvodu, který není duplicitní). V případě skládaného řešení ale v každém případě zůstanou 3 zcela funkční osmijádrové čipy a jeden, který lze v lepším případě použít jako šestijádrový, v horším jako čtyřjádrový a v nejhorším půjde na recyklaci. I v takovém případě ho ale může nahradit jiný osmijádrový modul a opět může vzniknout plně funkční 32jádrový procesor.

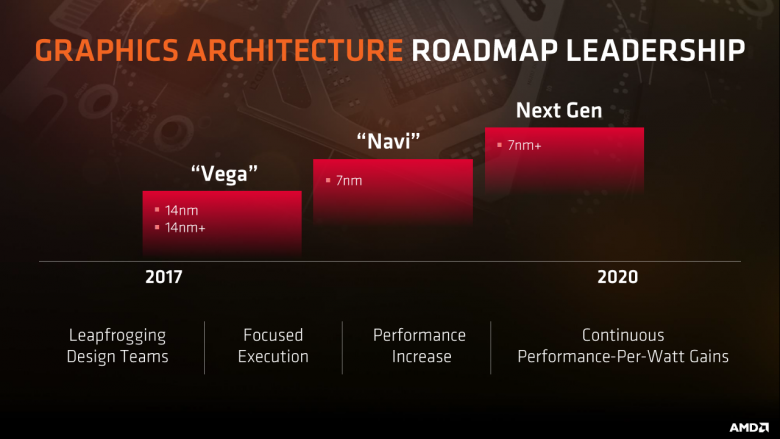

Spekuluje se, že trochu podobný přístup AMD nasadí i ve sféře grafických čipů, snad s architekturou Navi. Každý z menších čipů by nesl vlastní čip HBM paměti, která by v rámci všech částí byla sdílena s využitím HBCC. Lze si představit, že každý čip ponese ~2048 stream-procesorů, (tomu by odpovídalo 128 texturovacích jednotek), 32 ROP a 1024bit kanál HBM2, což by při stávajícím 14nm procesu měřilo kolem 250 mm² a na 7nm výrobě (za předpokladu 2,33× zmenšení) kolem 100 mm². HBM2 čip Hynixu dosahuje 92 mm², takže by teoreticky mělo být možné paměť integrovat i přímo na plochu grafického čipu. Samozřejmě by bylo věštěním z křišťálové koule, zda se tak stane v dohledné době, v budoucnu, nebo bude výhodnější setrvat u stávající integrace HBM vedle GPU jako na nynějších čipech.