Zen 2 zdvojnásobí kapacitu L3 cache na jádro

Architektura Zen v podobě samostatných procesorových modulů Zeppelin disponovala 512kb L2 na jádro a 2 MB L3 cache na jádro. Nižší řady mohly mít kapacitu L3 cache sníženou, ale toto byl základ, z něhož vycházely serverové i vyšší desktopové modely první generace Zen.

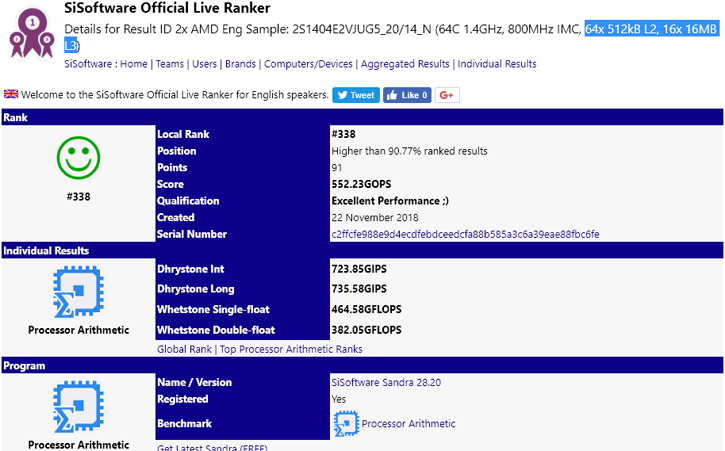

Výpis z databáze společnosti SiSoft ukázal, že firemní software detekuje nový Zen 2 / Epyc / Rome jakožto procesor s „64× 512kB L2, 16× 16MB L3“. Při 64 jádrech tedy zůstává 512kB L2 cache, ale při 16× 16 MB, tedy 256 MB, vychází 4 MB L3 cache na jádro. Což je dvojnásobná kapacita oproti první generaci. Údaj je samozřejmě jistý jen u tohoto konkrétního 64jádrového modelu. U nižších se opět může lišit. Jisté tedy je, že 64jádrový / 128vláknový Epyc Rome disponuje 256MB L3 cache.

Co zatím jisté není, je konfigurace a umístění cache. Výpis SiSoftu hovoří explicitně o 16× 16MB L3 cache. Mohlo by se tedy zdát, že cache je rozdělená na šestnáctiny a 64 jader : 16 je 4. To znamená 16 MB L3 cache pro 4 jádra. Na základě této logické konstrukce se objevují názory, že by Zen 2 mohl zakládat stejně jako Zen na čtyřjádrových CCX modulech. Rovněž se však objevují názory, že software SiSoftu nemusí umět rozložení cache správně interpretovat a pouze vychází z modelu, který platil pro první generaci. Jinými slovy, že zápis „16× 16MB L3“ jako jednoznačný důkaz o použití čtyřjádrových CCX sám o sobě neobstojí.

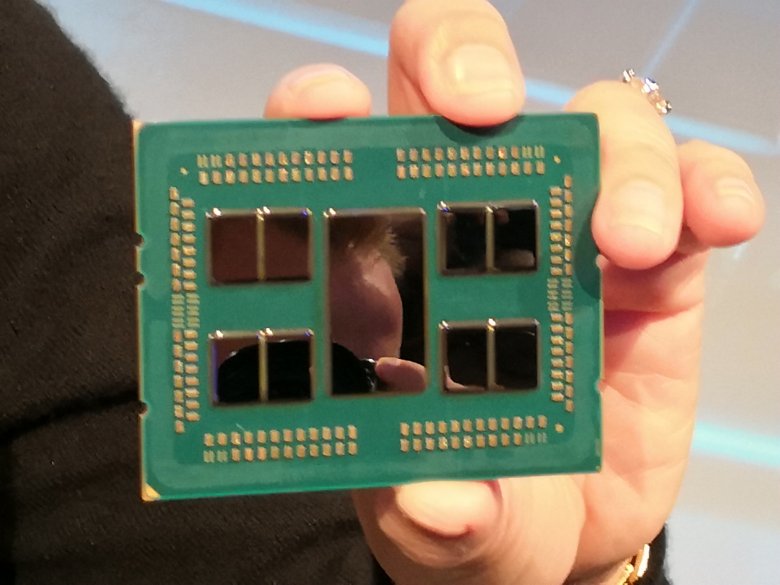

Podobné debaty se vedou také kolem umístění cache. Jedna názorová skupina předpokládá, že je součástí 7nm čipletů, druhá skupina předpokládá, že je L3 integrována v centrálním 14nm čipu. Je prakticky jisté, že centrální čip nějakou větší cache obsahuje, pravděpodobně právě 256MB. Není však jisté, zda L3 nebo L4. Pokud je v centrálním jádře L3, pak samozřejmě nebude v 7nm čipletech a ty končí vlastní L2 cache. Pokud je v centrálním jádře L4, pak by byl každý čiplet vybaven vlastní L3.

Pokud ještě zkombinujeme možnosti předchozích dvou odstavců, vychází nám poměrně dost možných scénářů. Některé jsou však méně pravděpodobné než jiné. Například by asi nedávalo valný smysl, aby L3 byla fyzicky segmentovaná na 16 samostatných 16MB bloků pro každý čtyřjádrový CCX, pokud by nebyla fyzicky umístěna v 7nm čipletech společně s CCX. Pokud by totiž byla v centrálním 14nm jádře, asi by nebyl důvod jí dělit na tolik separovaných dílů, které by byly přiřazené výhradně jedné konkrétní CCX umístěné v podstatě v jiném jádře. V takové situaci by dávala smysl cache více či méně monolitická, případně - pokud segmentovaná - tak vždy jeden celek pro každý 7nm čiplet (tzn. 8× 32 MB), nikoli aby byl každý čiplet připojen ke dvěma samostatným blokům cache.