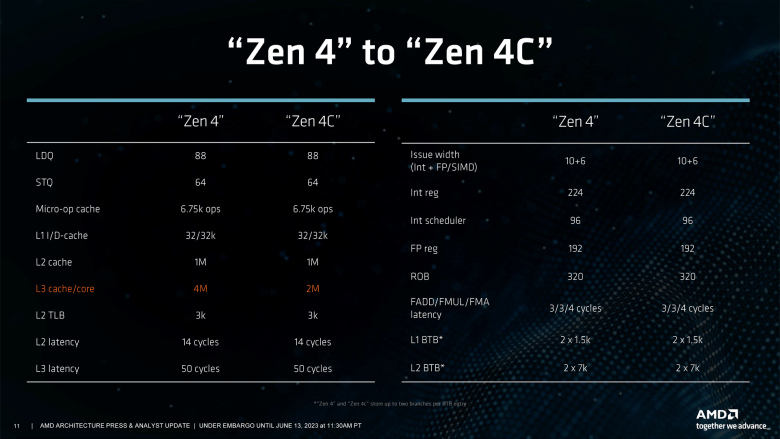

Zen 4c: L1, L2, μop, registr, scheduler, latence, instrukce - stejné jako Zen 4

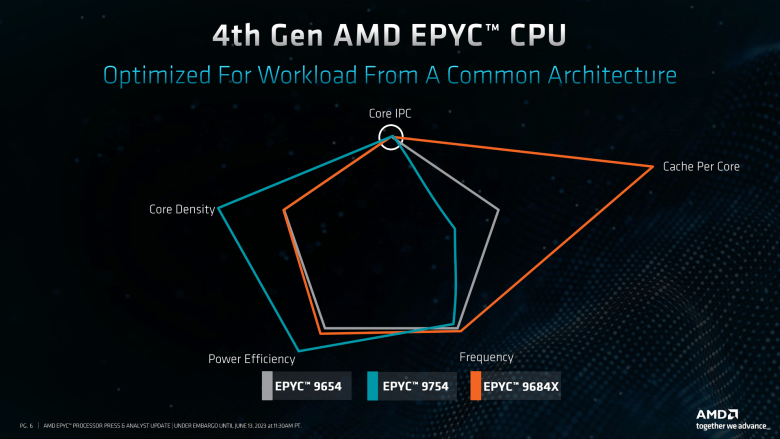

První diagram shrnuje odlišné zaměření klasických jader Zen 4 (Epyc Genoa, šedě), Zen 4 s V-cache (Epyc Genoa-X, oranžově) a Zen 4c (Epyc Bergamo, modře):

Zen 4c dosahuje o něco vyšší energetické efektivity a výrazně vyšší denzity. Kapacita L3 cache je proti standardnímu provedení poloviční a taktovací frekvence jsou jen mírně nižší. Základní takt je jen o 150 MHz nižší (2,25 GHz oproti 2,4 GHz). Možná jste si už ve včerejším článku všimli, že boost všech jader dosahuje (oproti ostatním Epycům) stejné hodnoty jako boost jednojádrový: 3,1 GHz, což je o 450 MHz méně (oproti 3,55 GHz) oproti 96jádrovému Zen 4. Nikoli tedy o 600 MHz, jak by se zdálo podle hodnot jednojádrového boostu, který v tomto segmentu (stejně) nenachází uplatnění. IPC samotného x86 jádra je totožné, celkové IPC však může být ovlivněno dalšími prvky jako jsou kapacita L3 cache na jádro, na druhou zmíněná vyšší datová propustnost L3 cache a nakonec i odlišná propustnost paměťové sběrnice na jádro (neboť propustnost je fyzicky stejná, ale jader, která se o ni dělí, je o třetinu více).

Plocha samotného x86 s L1+L2 cache je v případě Zen 4c o 35 % nižší než u Zen 4. Po započtení L3 cache vychází plocha potřebná pro integraci Zen 4c na jádro téměř o polovinu nižší. Tomu jsme se podrobně věnovali ve článku:

Pohled na celkový rozdíl v podobě procesoru ukazuje, že AMD de facto prací inženýrů nahrazuje to, co dříve zajišťovaly výrobní procesy: Snižování plochy křemíku (a tedy výrobních nákladů) při zvyšování celkového výkonu. Zatímco Epyc Genoa pro 96 jader potřebuje 12 5nm čipletů, Epyc Bergamo se při 128 jádrech vejde do 8 5nm čipletů.

Informačně nejbohatší (nebo vlastně nejchudší?) je tabulka uvádějící rozdíly mezi Zen 4 a Zen 4c. Jde o rozdíly z hlediska softwaru a zpracování úloh. Kromě kapacity L3 cache, která byla snížena na stejnou kapacitu, jakou mají APU (4 MB → 2 MB), jsou všechny hodnoty stejné. Cache se neliší ani latencemi a s výjimkou L3 ani kapacitou. Neliší se registr, scheduler ani latence instrukcí. Tento seznam zřejmě AMD vytvořila proto, že se dosud objevují (těžko říct odkud pocházející) zvěsti, že má Zen 4c menší L1/L2 cache nebo jinak ořezané některé prvky mající dopad na výkon. Nemá, z hlediska funkčnosti, IPC, instrukčních setů, registrů, scheduleru, latence instrukcí atd. je jádro stejné, pouze nepodporuje vysoké frekvence.

AMD