2nm proces TSMC bude stát $25 000 za wafer

V současnosti využívá většina nového hardwaru vznikajícího na linkách TSMC 5nm a 4nm proces. Nájezd na 3nm výrobu je pomalejší, přípravy nešly tak hladce, jak se očekávalo a někteří výrobci dali přednost o generaci staršímu 4nm procesu, jiní 3nm výrobě u Samsungu (ten jako první zavedl GAA / MBCFET technologii, zatím se však nezdá, že by mu to přinášelo nějakou hmatatelnou konkurenční výhodu).

Přestože se v médiích objevují zvěsti o tom, že zákazníkům vadí cena 3nm procesu TSMC, s ohledem na specifikace procesu lze za stejnou cenu z 3nm waferu vyrobit více čipů stejného návrhu než z 5nm waferu, takže problémem bude spíš kombinace výtěžnosti s rychlostí výroby.

TSMC dále chystá 2nm proces. Jako už tradičně bude prvním zákazníkem Apple. Různé zdroje uvádějí cenu za wafer kolem $25 000, což je samozřejmě vyšší cena než u předchozí technologie, ovšem procentuelní nárůst je nižší než je u procesů posledních let obvyklé:

| proces TSMC | cena | nárůst |

|---|---|---|

| 90nm | $2000 | - |

| 65nm | $2200 | +10 % |

| 40nm | $2600 | +18 % |

| 28nm | $3000 | +15 % |

| 20nm | $3700 | +23 % |

| 16nm | $4000 | +8 % |

| 10nm | $6000 | +50 % |

| 7nm | $10000 | +67 % |

| 5nm | $16500 | +65 % |

| 3nm | $20000 | +21 % |

| 2nm | $25000 | +25 % |

Zatímco 10nm, 7nm a 5nm proces přinesly cenové navýšení vždy o polovinu až dvě třetiny oproti předchozí generaci, mezigenerační zdražení 3nm a 2nm procesů se drží mezi pětinou a čtvrtinou, tedy na podstatně příjemnější úrovni. Je sice pravdou, že mezigenerační posuny co do denzity, úspory energie a zvyšování výkonu (frekvence) jsou generaci od generace slabší, ale to platilo i pro 10nm, 7nm a 5nm proces.

| EUV | zahájení výroby / tape-out | velkokapacitní výroba | ||

|---|---|---|---|---|

| TSMC | 7nm (N7) |  | leden 2017 | duben 2018 |

| 7nm (N7P) | ? | ? | ||

| 7nm EUV (N7+) | říjen 2018 | červen 2019 | ||

| 6nm | Q1 2020 | ? | ||

| 5nm (N5) | duben 2019 | H1 2020 | ||

| 5nm (N5P) | ? | 2021 | ||

| 4nm (N4) | Q3 2021 | Q1 2022 | ||

| 4nm (N4P) | H2 2022 | H2 2022 | ||

| 4nm (N4X) | H1 2023 | 2023 | ||

| 3nm (N3/N3B) | Q4 2021 | prosinec 2022 | ||

| 3nm (N3E) | ? | Q3 2023→Q2 2023 | ||

| 3nm (N3P) | ? | 2024 | ||

| 3nm (N3S) | ? | 2024 | ||

| 3nm (N3X) | ? | 2025 | ||

| 2nm (N2) | Q4 2024 | H2 2025 |

TSMC podle současných plánů nabídne 2nm proces v režimu zkušební výroby koncem roku 2024 a sériovou výrobu spustí ve druhém pololetí 2025. V segmentu osobních počítačů se tak nejspíš dočkáme 2nm čip(let)ů nejdříve v roce 2026.

| TSMC | |||

| proces | denzita | výkon | spotřeba |

|---|---|---|---|

| 7nm (N7) | +59 % vs. N10 | +35-40 % vs. N10 | -40 % vs. N10 |

| 7nm (N7P) | ? | +7 % vs. N7 | -10 % vs. N7 |

| 7nm+ (EUV / N7+) | +20 % vs. N7 | +10 % vs. N7 | -15 % vs. N7 |

| 6nm (N6) | +18 % vs. N7 | ? | ? |

| 5nm (N5) | +80 % vs. N7 | +15 % vs. N7 | -30 % vs. N7 |

| 5nm (N5P) | ? | +7 5 % vs. N5 | -10 % vs. N5 |

| 4nm (N4) | +6 % vs. N5 | téměř beze změny | beze změny |

| 4nm (N4P) | +6 % vs. N5 | +11 % vs. N5 +6 % vs. N4 | -22 % vs. N5 |

| 4nm (N4X) | ? | +15 % vs. N5 @1,2V +4 % vs. N4P @1,2V | ? |

| 3nm (N3) | +70 % vs. N5 2,9× vs. N7 | +10-15 % vs. N5 +32 % vs. N7 | -25-30 % vs. N5 |

| 3nm (N3B) | +60 % vs. N5 2,9× vs. N7 | +10-15 % vs. N5 +32 % vs. N7 | -35 % vs. N5 -43 % vs. N7(?) |

| 3nm (N3E 3-2 Fin) 3nm (N3E 2-2 Fin) 3nm (N3E 2-1 Fin) | +18 % vs. N5 +39 % vs. N5 +56 % vs. N5 | +33 % vs. N5 +23 % vs. N5 +11 % vs. N5 | -12 % vs. N5 -22 % vs. N5 -30 % vs. N5 |

| 3nm (N3P) | +4 % vs. N3E | +10 % vs. N3E | ? |

| 3nm (N3S) | ? | ? | ? |

| 3nm (N3X) | +4 % vs. N3P | +15 % vs. N3P | ? |

| 2nm (N2) | +10% vs. N3 | +13 % vs. N3E 2-1 | -33 % vs. N3E 2-1 |

| 2nm (N2P) | +9-13 % vs. N2 | +10-12 % vs. N2 | ? |

Od 2nm procesu se pak neočekává výraznější posun co do denzity. To je velký rozdíl oproti 3nm procesu, který sliboval 70%, ale nakonec - viz N3B - dosáhl přinejlepším 60%. TSMC nedávno předložila výsledky časného vzorku ARM A715 vyrobeného 2nm procesem, který vykazuje 13% nárůst frekvencí oproti N3E 2-1 Fin (při stejné spotřebě) nebo o 33 % nižší spotřebu při stejném taktu.

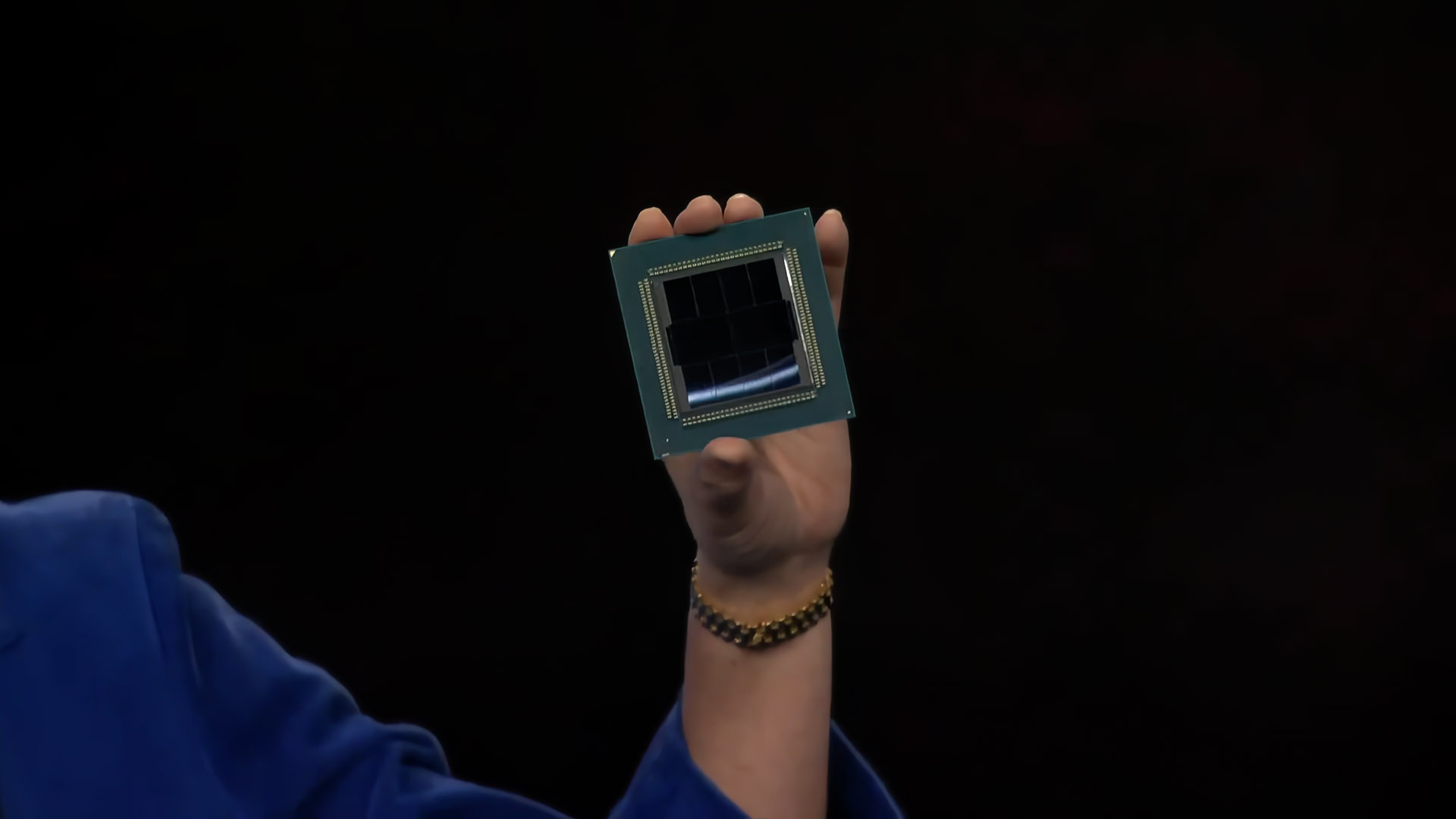

Proces N2 je první implementací GAA technologie ze strany TSMC, proces N2P pak doplní ještě tzv. backside power delivery, což umožní dále ušetřit nějakou plochu, zvýšit takty (nebo snížit spotřebu, ale o kolik, to zatím není známo). S touto variantou procesu se počítá pro výkonnější čipy a bude dostupná zhruba půl roku po základní verzi.