AMD opět hovoří o Barceloně

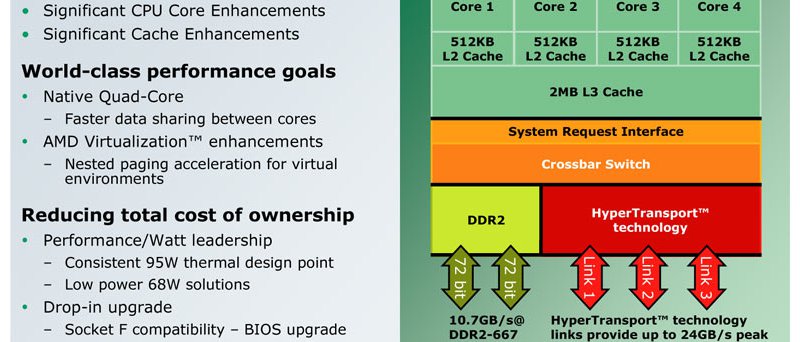

Začneme obrázkem, kde AMD srovnává čtyřjádrový Opteron „Barcelona“ se čtyřjádrovým Xeonem „Clovertown“, o němž již dříve firma tvrdila, že jej „Barcelona“ překoná o 40 %. Jako obvykle AMD vyzdvihuje integrovaný paměťový řadič a HyperTransport a kritizuje Intelovu Front Side Bus (které v poslední době Intel stále častěji říká spíše PSB – Processor System Bus). A protože „Clovertown“ není nativně čtyřjádrový, ale jde o dva dvoujádrové čipy v jednom procesoru, vzniká tak dle AMD úzké hrdlo („bottleneck“) v komunikaci mezi oběma čipy. Když například potřebuje jádro 1 něco od jádra 3, musí jít přes sběrnici a tedy její rychlostí, zatímco u „Barcelony“ probíhá taková výměna dat rovnou skrze cache za přispění Crossbar switche. Sluší se zmínit, že tento Crossbar switch je navržen s výhledem na vytvoření nativně osmijádrového procesoru.

Za zmínku ještě stojí komunikace mezi jednotlivými úrovněmi cache. Jak asi víte, již nějaký čas používá Intel tzv. „inclusive“ cache, kdy celá L1 je obsažena také v L2. To u AMD procesorů není a navíc v „Barceloně nebude“ v případě, že jedno jádro bude potřebovat data z L1 cache jiného jádra, budou moci tato putovat z L1 rovnou do L3 a nikoli přes L2 cache. Vedle toho v případě zaplnění L1 cache budou do L2 putovat nejprve data nejstarší, u nichž se dá předpokládat, že už nebudou tolik potřeba.

Další obrázek popisuje to, co už známe. „Barcelona“ přijde s vylepšenou správou napájení, v AMD se totiž snažili se spotřebou něco udělat a vymysleli nezávislé taktování jednotlivých jader při různém vytížení. Zatímco v současných Opteronech jsou obě jádra tak rychlá, jak potřebuje nejzaměstnanější jádro, v „Barceloně“ se bude každé jádro zpomalovat nezávisle na ostatních dle vlastních potřeb a dokonce bude nezávisle taktován i integrovaný severní můstek (jinými slovy především paměťový řadič). Má to jedinou drobnou vadu na kráse: napájení celého procesoru se i tak bude řídit nejrychleji běžícím jádrem (každé jádro bude mít pět různých stavů vytížení a napětí bude dodáváno podle stavu nejvytíženějšího jádra). Koneckonců „Barcelona“ bude umět vypínat i jednotlivé nevyužívané části procesoru (což ale není dnes žádná závratná novinka).

Opět něco, co již víme, ale co potěší natolik, že je to vhodné zopakovat. Procesory pro socket AM2 i AM2+ budou navzájem kompatibilní, AM2 procesor půjde strčit do socketu AM2+ a naopak. Samozřejmě procesor AM2+ v AM2 socketu, ani AM2 v AM2+ socketu nevyužijí rychlejší HyperTransport 3.0, ale oba budou mít dvoukanálový DDR2 paměťový řadič a tedy není potřeba žádná změna v paměťovém subsystému desky. Dlužno též dodat, že AM2+ procesor bude mít posazen do AM2 socketu trochu vyšší spotřebu, než kdyby byl v socketu AM2+, protože zde nebude fungovat ono nezávislé taktování jednotlivých jader a paměťového řadiče.

Nakonec se nenápadně podívejme ještě dál do budoucnosti, kde už se rýsuje nástupce „Barcelony“ s krycím jménem „Shanghai“. Ten bude prakticky jen určitým vylepšením „Barcelony“ právě v „oblasti čtyř jader“ a na trhu bychom jej měli zahlédnout v průběhu příštího roku. Asi nebudeme muset být nijak moc optimističtí, abychom se mohli domnívat, že už bude vyráběn 45nm procesem, což by mohlo znít slibně ze dvou důvodů: může se zvětšit L3 cache, případně může také dojít na nedávnou skoro kacířskou myšlenku relativně jednoduchého vytvoření osmijádrového procesoru umístěním dvou takovýchto čtyřjádrových kousků křemíku „pod jednu střechu“ a propojením přes HyperTransport. Ale to už opravdu jen hádáme, samotná křišťálová koule v této fázi zobrazuje už jen zrnění.