Detailní mikrosnímky IO čipletu Ryzenu a Epycu ukazují „hodně pamětí“

Zvěst o L4 cache zřejmě vznikla špatným výkladem informace, že jádra obsahují (snad) stovky megabytů SRAM. Což si není těžké představit jako nějakou uniformní jednolitou L4 cache. Jak ukazuje nový detailnější rozbor (jednomu jsme se věnovali loni, ale ten nebyl zdaleka takto podrobný), paměti je v čipletech opravdu hodně, ale podstatná část je rozptýlena v rámci různých bufferů, cache a registrů jednotlivých řadičů.

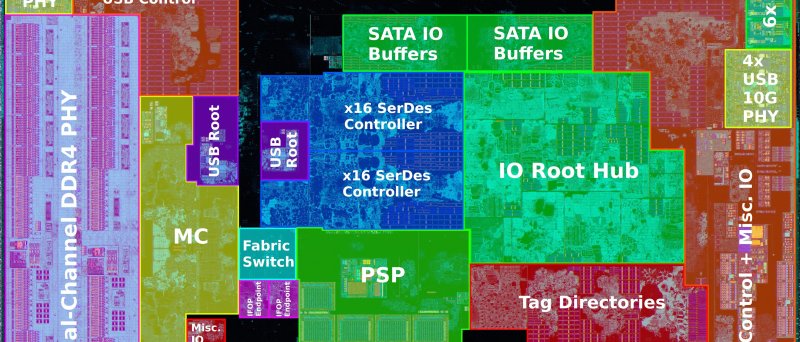

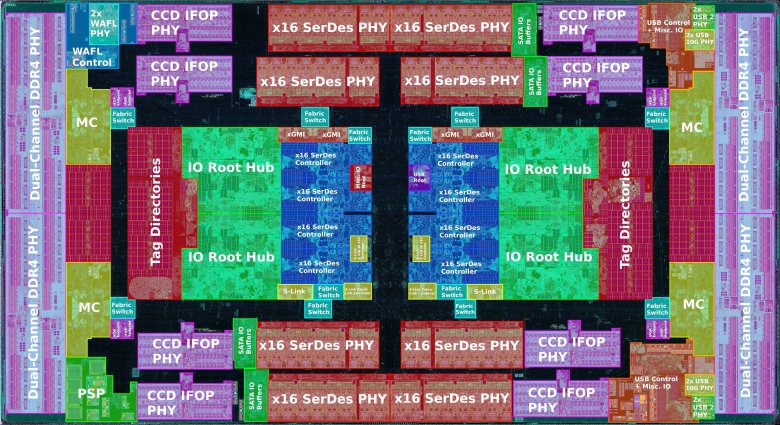

Rozbor připravil VLSI inženýr Nemez na základě mikrosnímků, které pořídil již proslulý „leštič a fotograf“ křemíku, FritzchensFritz. Začněme u centrálního čipletu z Epycu (Threadripperu), tedy toho většího, který obsluhuje až osm procesorových 7nm čipletů:

V první řadě malé upozornění: snímky mají v plném rozlišení (tj. po rozkliknutí) kolem 3 MB každý. Což je ale nutné, aby na nich bylo něco vidět. Začali jsme u paměti, tak se nejdříve zaměříme na ni. SRAM (ať už jakkoli využitou) na snímcích poznáte docela snadno - jde o tmavší pravidelné obdélníčky nebo čtverečky, hlavně v centrálních blocích a jejich okolí. Jsou všudypřítomné a je jich hodně. Pokud bychom si měli seřadit, jaké prvky zabírají z plochy jádra nejvíce, byla by to na prvním místě fyzická rozhraní (PHY), tedy části čipu, jejichž účelem je vyvést z křemíku na pouzdro kontakty různých sběrnic (DDR4, PCIe - tj. x16 SerDes, externí Infinity Fabric pro čiplety - tj. CCD IFOP a další drobnější jako SATA, USB a podobně). Na druhém místě by nejspíš figurovala právě SRAM a asi těsně za ní sběrnice Infinity Fabric, možná na podobné úrovni jako logika řadičů, která se zdá být oproti ostatním jmenovaným prvkům v minoritě.

Všimněte si například, kolikrát je MC (logika paměťového řadiče, žlutě) menší než samotné DDR4 rozhraní (DDR4 PHY, světle modrofialově). Na tom lze docela hezky ilustrovat, co vedlo ke vzniku pamětí jako HBM, které právě PHY minimalizují.

Pak tu mámě několik polí se zajímavým značením. Tak třeba téměř vlevo nahoře je „WAFL control“ a „WAFL PHY“. Ač tím jistě mnohé čtenáře zklamu, nejde bohužel o rozhraním, kterým byste váš Epyc nebo Threadripper mohli krmit waflemi. Jde o něco malinko jiného. Pro vysvětlení ocituji část textu z článku, který jsme vydali při uvedení této generace procesorů:

Původní Epyc teoreticky disponoval celkem 128 PCIe linkami (osmi bloky ×16), ale jejich využití bylo v jednom ohledu problematické - žádná běžná deska nenabídla těchto 128 linek v PCIe slotech. Důvodem je BMC neboli Baseboard Management Controller. V praxi jde o řídící čip osazený na většině serverových desek, který je pro účely komunikace s procesorem vybaven PCIe ×1 linkou. Právě tato jedna linka znamenala, že byl z hlediska využitelnosti v socketu vyřazen jeden PCIe ×16 blok, kam byla tato linka připojena. Bylo samozřejmě možné zbývajících 15 linek rozdělit mezi nějaké řadiče na desce, ale ty nemusely být vždy žádané - navíc po vyčerpání tří zbývajících ×4 zůstala ještě jedna ×2 a jedna ×1 linka, kde možností využití příliš nebylo. Epyc Rome proto na úroveň procesoru doplní bonusovou PCIe ×1 linku navíc, takže i po osazení BMC zůstane procesoru krásných kulatých 128 PCIe linek (plných osm bloků ×16). Toto řešení se zdá být dokonce elegantnější než přístup Intelu, který BMC připojuje k lince vyvedené z externího čipsetu. Tím sice ochrání „celistvost násobků“, ale na připojení externího čipsetu spotřebuje část linek, jimiž je vybaven procesor. |

Čiplet Zen 2 Epycu (Rome) je fyzicky vybavený dvěma těmito samostatnými PCIe ×1 linkami a ty jsou ve schématu označené právě jako WAFL.

Naopak úplně dole a téměř vlevo najdete PSP. Opět nejde, jak by se leckdo mohl těšit, o integrovaný PlayStation Portable, ale o uživatelsky významně nudnější Platform Security Processor, bezpečnostní koprocesor postavený na ARM architektuře.

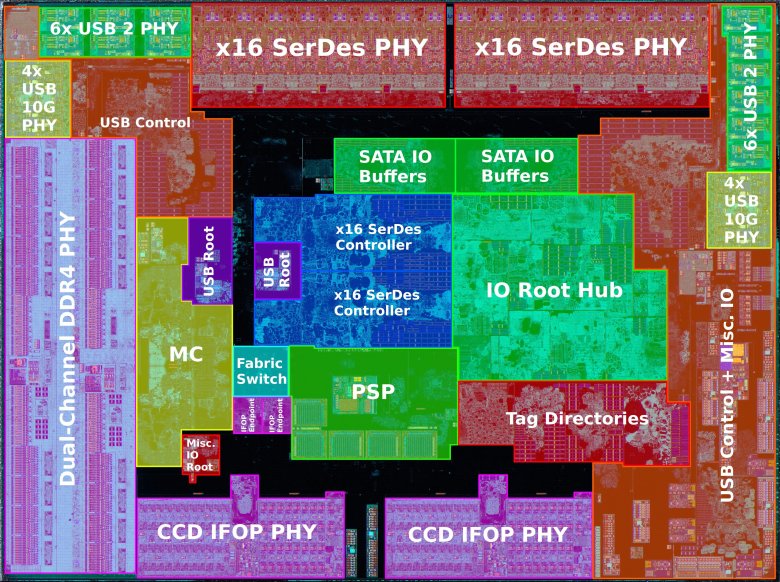

Nyní IO čiplet desktopového Zen 2, který najdete ve všech AM4 Ryzenech 3000 bez grafiky. Platí pro něj, co bylo řečeno výše: Velké rozhraní DDR4 PHY s menším (žlutým) řadičem, velké rozhraní PCIe (nahoře červeně) a o něco menší (dole fialově) rozhraní pro připojení procesorových 7nm čipletů (externí Infinity Fabric). S čím se nelze zcela ztotožnit, je označení USB řadičů (USB Control), které není zvlášť v pravé části čipu graficky odděleno od dalších rozhraní (Misc. IO). Vytváří to dojem, že plocha věnovaná implementaci USB je enormní. Ve skutečnosti je to naopak a téměř vše cihlově červené, co leží níže než linie vymezená spodním okrajem žluté kostičky s popisem „4× USB 10G PHY“, je spíše to „Misc. IO“, tedy různá další rozhraní. Všimněte si, že USB rozhraní v levém horním rohu žádné takové struktury nepotřebuje - je to tím, že s USB nijak nesouvisejí a mohly by od něj být graficky oddělené. To je ale snad jediná drobná výtka, kterou ke schématům mám - jde o velmi kvalitní práci, která se nedá srovnat s tím, co se objevovalo v souvislosti s „rozbory“ mikrosnímků APU Renoir, jejichž autoři si nevšimli ani toho, že nejde o mikrosnímky, ale malůvku z editoru.

Závěrem jen pro úplnost: Snímky obou čipletů nejsou zobrazené vzájemně ve stejném měřítku. Oba jsou roztaženy na stejnou šířku, aby i bez rozkliknutí bylo vidět co nejvíce detailů.