Extrémní verze 4nm procesu TSMC dosáhne přinejmenším taktů 3nm výroby

Když se v plánech TSMC objevila první verze 4nm procesu, nabízela se otázka: Proč? Technologie totiž nepřinášela nic jiného než docela zanedbatelný 6% nárůst denzity, ovšem posun výkonu ani pokles spotřeby se konat neměl. Posun z 5nm na 4nm výrobu je tedy alespoň 3× menším rozdílem než posun ze 7nm na 6nm výrobu. V říjnu však TSMC přišla s ohlášením podstatně vylepšené verze 4nm výroby, která měla oproti 5nm procesu o 11 % zvýšit výkon nebo o 22 % snížit spotřebu. Tím už se blížila provozním vlastnostem 3nm procesu.

| TSMC | |||

| proces | denzita | výkon | spotřeba |

|---|---|---|---|

| 7nm (N7) | +59 % vs N10 | ? | -40 % vs. N10 |

| 7nm (N7P) | ? | +7 % vs. N7 | -10 % vs. N7 |

| 7nm+ (EUV / N7+) | +20 % vs. N7 | +10 % vs. N7 | -15 % vs. N7 |

6nm (N6) | +18 % vs. N7 | ? | ? |

| 5nm (N5) | +80 % vs. N7 | +15 % vs. N7 | -30 % vs. N7 |

| 5nm (N5P) | ? | +7 5 % vs. N5 | -10 % vs. N5 |

| 4nm (N4) | +6 % vs. N5 | téměř beze změny | beze změny |

| 4nm (N4P) | +6 % vs. N5 | +11 % vs. N5 +6 % vs. N4 | -22 % vs. N5 |

| 4nm (N4X) | ? | +15 % vs. N5 @1,2V +4 % vs. N4P @1,2V | ? |

| 3nm (N3) | +70 % vs N5 | +10-15 % vs. N5 | -25-30 % vs. N5 |

| 3nm (N3E) | ? | + | + |

| 2nm (N2) | +70% vs. N3? | ? | ? |

Nyní do seznamu chystaných novinek doplňuje výrobce N4X variantu, která je zaměřená na HPC segment (HPC míněno ve smyslu TSMC, tedy veškerý výkonný hardware). Proces je primárně optimalizován pro dosažení vyšších taktovacích frekvencí (i lehce na úkor spotřeby), takže při stejném napětí s 5nm procesem (konkrétně 1,2V) bude schopný dosáhnout o 15 % vyšších taktů. Na rozdíl od 5nm procesu ale podporuje i napětí nad 1,2V, takže výrobci mohou jít ještě dál.

Těchto optimalizací TSMC dosáhla přepracováním kovových prvků back-endu a implementací kondenzátorů kov-izolant-kov s vysokou hustotou. Společnost předpokládá, že proces bude nasazen na produktech o TDP v řádu stovek wattů, v extrémních případech až ~1000 wattů, které integrují stovky MB SRAM. Na N4X lze vyrábět návrhy vyvinuté pro 5nm proces bez potřeby přepracování.

| EUV | zahájení výroby / tape-out | velkokapacitní výroba | ||

|---|---|---|---|---|

| Samsung | 7nm LPE (1. gen.) | ? | nezahájena | |

| 7nm LPP (2. gen) | říjen 2018 | červen 2019 | ||

| 7nm (3. gen) | ? | ? | ||

| 6nm LPP | duben 2019 | H2 2019 | ||

| 5nm LPE | 4. 2019 / H2 2019 | H1 2020 | ||

| 5nm LPP | 2019? | 2021 | ||

| 4nm LPE (původní) | ? | 2020/21 zrušen | ||

| 4nm LPP (původní) | ? | 2022 zrušen | ||

| 4nm LPE | ? | 2022 | ||

| 4nm LPP | ? | ? | ||

| 3nm (3GAE) | Q4 2021 | H1 2022 | ||

| 3nm (3GAP) | ? | 2023 | ||

| TSMC | 7nm (N7) |  | leden 2017 | duben 2018 |

| 7nm (N7P) | ? | ? | ||

| 7nm EUV (N7+) | říjen 2018 | červen 2019 | ||

| 6nm | Q1 2020 | ? | ||

| 5nm (N5) | duben 2019 | H1 2020 | ||

| 5nm (N5P) | ? | 2021 | ||

| 4nm (N4) | Q3 2021 | Q1? 2022 | ||

| 4nm (N4P) | H2 2022 | 2023? | ||

| 4nm (N4X) | H1 2023 | ? | ||

| 3nm (N3) | Q4 2021 | H2 2022 | ||

| 3nm (N3E) | ? | H2 2023 | ||

| 2nm (N2) | 2023? 2024? | 2024? 2025 |

Všechny tyto údaje zní velmi zajímavě, ovšem trochu překvapivý může být fakt, že společnost nepředpokládá zahájení rizikové výroby dříve než v první polovině roku 2023. Což znamená, že velkokapacitní výroba nejspíš nenastane dříve než ve druhém pololetí 2023, tedy stejně jako výkonná verze 3nm procesu (N3E), která by neměla být v žádném technologickém ohledu horší.

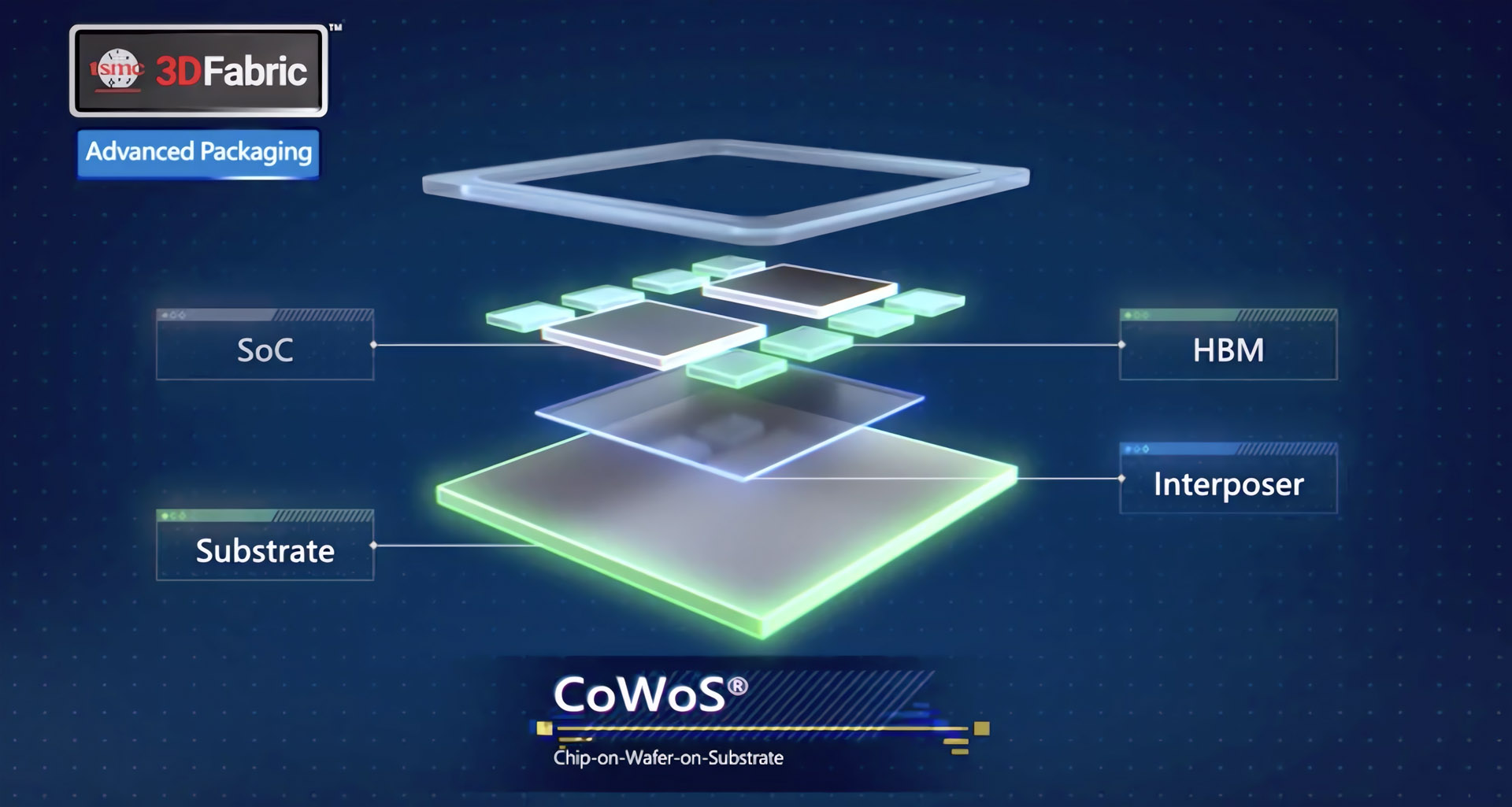

Proč tedy TSMC tento proces připravila? Z nějakého důvodu v něm vidí smysl. Hypotetickými důvody mohou být například příliš vysoká cena N3E, kvůli které dají někteří zákazníci přednost N4X. Případně nedostatečné výrobní kapacity N3E nebo jeho možné zpoždění. Musíme však mít na paměti, že ve druhé polovině roku 2023 (tj. prakticky 1,5-2 roky) budou podstatně rozšířenější čipletové produkty. Je tedy možné, že se v HPC segmentu na nějakém produktu klidně sejdou čiplety vyrobené N4X a N3E procesem.

TSMC