AMD Infinity Fabric, víc než jen nový HyperTransport

Při představení procesorů Ryzen padla několikrát zmínka o sběrnici Infinity Fabric, zákulisně se o ní mluvilo i v souvislosti s grafickými procesory Vega. Protože jsme o ní zatím nehovořili, je načase to napravit.

Ať už jde o přesuny dat na úrovni čipu nebo mezi čip vzájemně, je potřeba mít pro daný účel implementovanou nějakou sběrnici. U procesorů AMD před lety vsadila na HyperTransport, což je dosud ve světě IT poměrně známý pojem, ale faktem je, že ať už jde o procesory, grafické čipy nebo APU, nevyužívaly žádné produkty AMD pouze sběrnici jednoho typu. Většinou byly datové přesuny v jádře realizované formou více různých protokolů. To bylo více-méně evolučním důsledkem, kdy se během vývoje nových produktů řešilo to, co bylo třeba. Pokud někde vznikl nárok na rychlejší přesun dat, byl nasazen rychlejší protokol. Kde nebylo třeba, nebyl. Jenže v okamžiku, kdy dochází k celkovému přepracování čipu, přináší řada protokolů komplikace. Je třeba je všechny inovovat, aby odpovídaly novým požadavkům, je třeba zajišťovat vzájemnou kompatibilitu, synchronizaci.

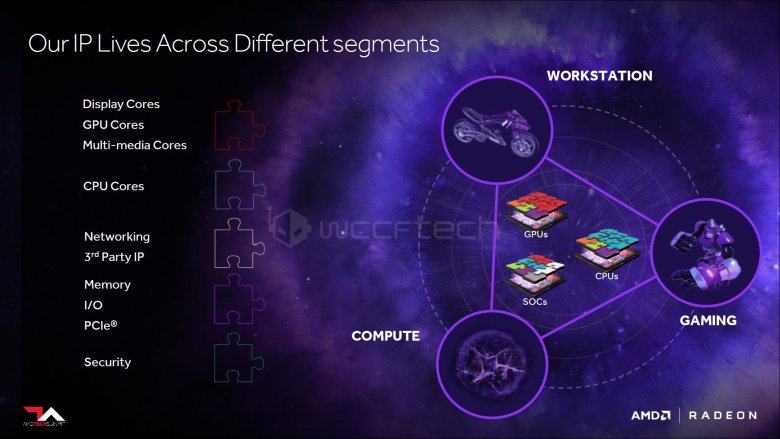

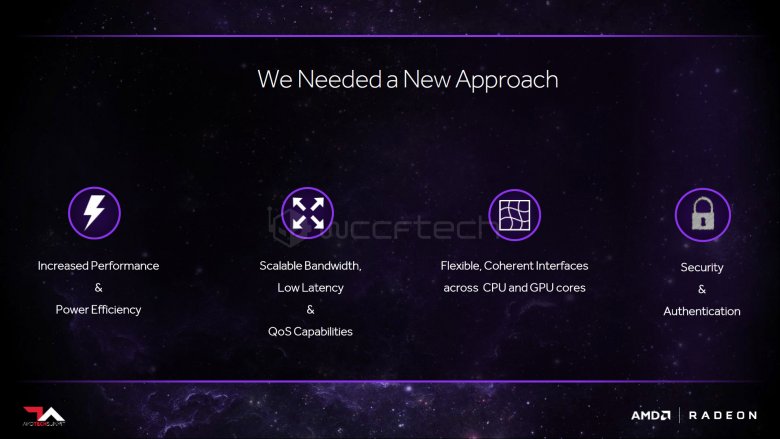

Proto se AMD rozhodla k rezolutnímu kroku: Vyvine jednu univerzální sběrnici, která bude škálovatelná, která bude schopná zajistit jak vzájemnou komunikaci jednotlivých částí čipu, tak komunikaci externí (čipů mezi sebou) a kterou bude možné použít nejen pro procesory, tak i grafické čipy a samozřejmě i APU, která obojí spojují. Označení pro tuto sběrnici je Infinity Fabric a bude (či už je) použitá ve všech produktech s jádry architektury Zen a Vega.

Infinity Fabric - krom čistšího přístupu a široké kompatibility - přináší jednu vlastnost, kterou předešlé sběrnice nenabízely. Je široce škálovatelná, takže ji lze dimenzovat na datovou propustnost, která plně odpovídá požadavkům nejrychlejších pamětí. Což v případě GPU Vega 10 bude 512 GB/s s HBM. Na druhé straně lze Infinity Fabric uzpůsobit nízkým požadavkům mobilních APU a zredukovat ji na nízké desítky GB/s.

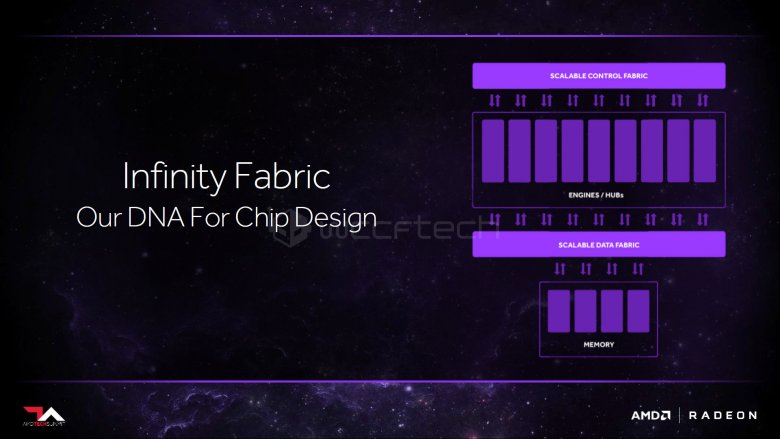

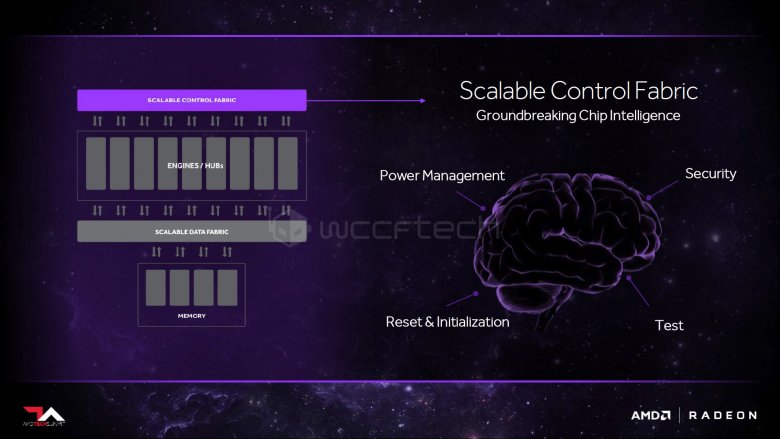

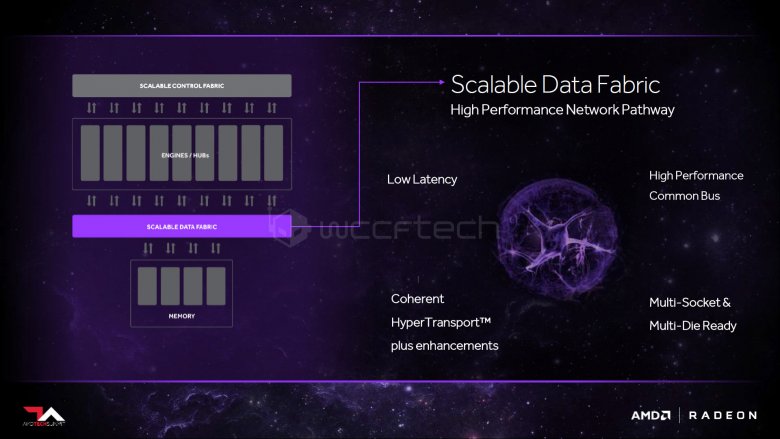

Infinity Fabric nepočítá jen s přesuny dat, ale i s řízením čipu. AMD ji v tomto ohledu rozděluje na dvě části - Scalable Data Fabric, která se bude starat o zásobování a přesuny dat ke zpracování a Scalable Control Fabric, která se postará o přenosy příkazů, řízení čipu, zabezpečení, řízení spotřeby a podobně.

Maurice Steinman, který má v AMD na starosti SoC, uvedl příklad dopadu, jaký má sběrnice na vývoj čipů: Pokud se v rané fázi vývoje nového SoC rozhodli pro změnu na úrovni sběrnice, znamenal tento zásah práci na několik měsíců. S Infinity Fabric lze změnu provést za několik hodin.

Dopady na charakter koncových produktů zatím není snadné hodnotit. Výrazné budou obzvlášť v profesionálním segmentu, kde se počítá s užším propojením grafických čipů a procesorů, ale zajímavý přínos by mohl být i ve světě APU. Těsnější propojení grafické a procesorové části může rozšířit možnosti HSA. Ve světě grafických čipů došlo k nasazení Infinity Fabric paralelně s celkovým přepracováním paměťové infrastruktury, takže nebude možné smysluplně rozlišit, jaký přínos má jedna změna a jaký druhá.