Intel Xeon Phi - Knights Corner nese 32 MB L2 cache

Hned v úvodu je třeba předeslat, že ačkoli se během dlouhé vývojové pouti architektury Larrabee hovořilo o možnosti vypuštění x86 kompatibility, nestalo se tak. Knights Corner / Xeon Phi stále staví na x86 kompatibilních výpočetních jednotkách. Těch prý 22nm čip obsahuje 64 (ačkoli některé zprávy mluvily o fyzickém počtu 62).

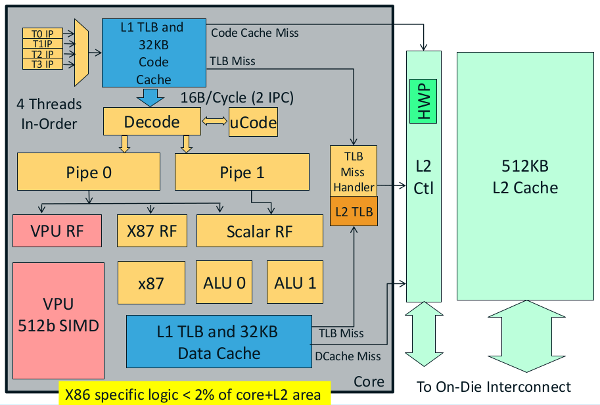

Pokud přeskočíme až do spodní části diagramu, můžeme si všimnout, že se Intel chlubí velmi nízkým procentem z plochy jádra, které okupuje logika zajišťující x86 kompatibilitu. Nemůžeme ovšem opomíjet, že ta necelá 2 % jsou vypočtena nikoli z plochy samotného procesorového jádra, ale z plochy, kterou zabírá jádro včetně L2 cache. Vzhledem k tomu, že neznáme rozměry jednotlivých výpočetních bloků, toto číslo nemá přílišnou vypovídací hodnotu (odhadujeme, že plocha jádra bude dosahovat zhruba 100 - 200 % plochy zabrané L2 cache - tak tomu alespoň je u jedoduchých x86 čipů, jako jsou Atom či Bobcat).

Samotné jádro se základním konceptem podobá prvnímu z Pentií - jde o superskalární in-order architekturu s dvěma pipelines. Ostatní už se liší - především o 512bitové vektorové jednotce Pentium ani neslyšelo. Dále obsahuje (celkem) 64kB L1 cache, která se rovnými polovinami dělí na datovou a instrukční část. Za L2 cache budeme muset z jádra ven:

Každé je spojeno s 512 kB - tento půlmegabajt se údajně nesčítá mezi ostatní (na rozdíl od architektury Intel Core nebo čerstvě představeného AMD Jaguar). 512 kilobajtů pro 64 jader nám dává celkových 32 MB cache. Pokud nemáte srovnání a nejste si jisti, zda je to hodně nebo málo, pak vás můžeme odkázat na rozbor architektury GCN čipu AMD Tahiti, který nás překvapil kolem 12 MB celkové integrované paměti. Je sice pravdou, že současný Xeon Phi už není grafickým čipem - spíše mnohojádrovým procesorem (a u procesorů je vyšší kapacita cache na jádro běžná), nicméně si AMD Tahiti s Intel Phi budou konkurovat v HPC sféře a jejich srovnání tak není zcela mimo mísu.

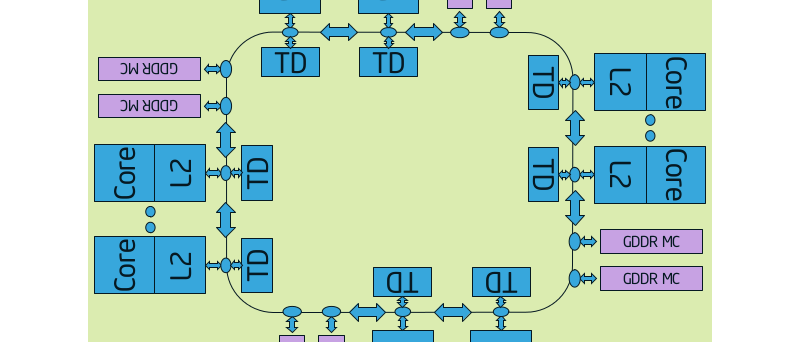

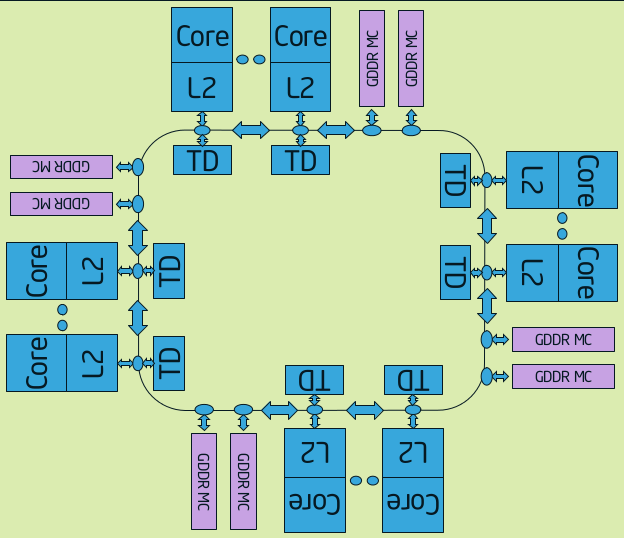

Ostatně i použití GDDR5 ukazuje na grafický prapůvod Larrabee - případně na prostý fakt, že jde o nejdostupnější a cenově nejvýhodnější rychlé paměti s podporou ECC :-). Řadiče a bloky L2 cache jsou společně propojené prstencovou sběrnicí - jejíž existence byl snad vůbec první parametr, který ohledně Larrabee před lety prosákl na veřejnost. Tento koncept umožňuje spojení až 64 jader a 8 paměťových řadičů plus řady PCIe rozhraní. Na další detaily si ještě budeme muset počkat.