Cache, ROP a paměťový subsystém

Kapitoly článků

Celý systém bychom mohli rozdělit na tři celky: Paměťovou sběrnici, hub a systém cache, který zásobuje daty kritické části GPU.

Paměťová sběrnice

Krom čipu R600 jsme byli zvyklí, že ATI / AMD od roku 2002 osazovala veškerý high-end a vyšší mainstream 256bit paměťovou sběrnicí. Protože v současné době rychlost dostupných pamětí stagnuje (od vydání Radeonu HD 4870 v červnu 2008 - tedy za 3,5 roku - vzrostla jen o 50%), nebyla jiná možnost, než zvolit alternativní cestu a tou byla (s přihlédnutím k dostačující ploše GPU) širší sběrnice.

- související informace najdete ve článku Končí éra pamětí GDDR5?

Nároky na paměťovou sběrnici jsou závislé na celé řadě faktorů, ale pro jednoduchost vezmeme v potaz jen několik základních:

- architektura (optimalizace, kompresní algoritmy...)

- celkový výkon konkrétního čipu

- konkrétní aplikace

- cílené rozlišení

S příchodem Radeonů HD 5800 před dvěma lety sice dvojnásobně vzrostl počet ROP jednotek (které jsou samy o sobě jedním z nejvýraznějších konzumentů dostupného pásma), ale samotná paměťová propustnost zdvojnásobená nebyla. To mělo za následek mírně zvýšenou limitaci ze strany paměťové sběrnice, která se projevovala zhruba 3% nárůstem výkonu při 10% přetaktování pamětí. Nešlo tedy o hlavní limitující faktor výkonu, nicméně se projevoval výrazněji než u předešlé generace.

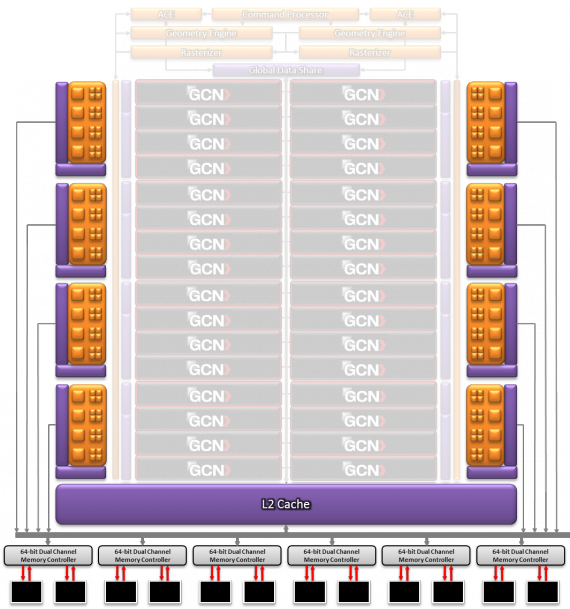

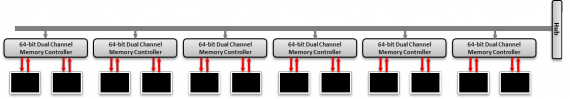

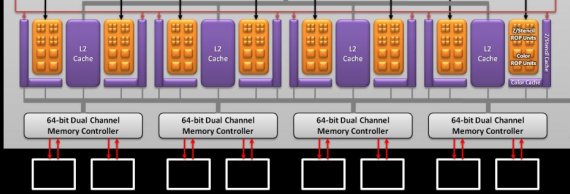

384bit řadič GPU Tahiti zásobuje šest 64bit kanálů, šest bloků L2 cache (detaily níže) a připojuje hub,

který distribuuje data mezi méně náročné klienty

Celkové navýšení výkonu čipu má samozřejmě za následek vyšší vytížení ROP, které ale bez adekvátního navýšení datové propustnosti nemohou efektivně fungovat. Lze předpokládat, že hypotetická 256bit paměťová sběrnice by se na čipu Tahiti mohla stát primárním limitujícím faktorem výkonu. Na jednu stranu se sice může zdát, že 5% nárůst výkonu při zrychlení sběrnice o 10% stále není žádný extrém - na druhou stranu to znamená, že výkonnostní potenciál čipu (tedy tranzistory = výrobní náklady) nejsou využité a přicházejí vniveč.

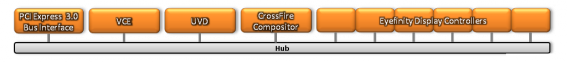

Hub

Na části řadiče určené pro nižší datové transfery se v zásadě nic nemění. Méně nároční klienti získali samostatný hub (již s příchodem GPU RV770), aby kvůli nim zbytečně nenarůstala komplexnost primárního řadiče. Původně byl na hub napojený PCIe řadič, logika pro CrossFire, UVD procesor a display controller pro obrazový výstup. S generací prvních DirectX 11 Radeonů se k původním dvěma přidaly až čtyři další výstupy pro Eyefinity a generace Radeonů HD 7000 na hub napojila ještě VCE procesor pro hardwarovou kompresi videa (více v kapitole 9).

ROP (RBE)

Pro AMD v současnosti nebyla jiná cesta, než problém datové propustnosti vyřešit rozšířením sběrnice. Všimněte si, že ROP jednotky nejsou fixně vázané na paměťové kanály, takže AMD mohla přejít z 256bit na 384bit rozhraní aniž by byla nucena změnit počet ROP. Protože se společnosti vyplatilo kvůli této změně vyvinout nové asociativní rozhraní mezi ROP a paměťovými kanály, můžeme předpokládat, že takový způsob řešení nabídl lepší poměr výkon / tranzistor než prosté použití 48 ROP, které by dosavadní architektura při implementaci 384bit sběrnice vyžadovala. Podobnou flexibilitu umožňovala naposledy architektura R5xx (kdy například Radeon X1950 PRO postavený na čipu RV570 kombinoval 12 ROP s 256bit sběrnicí).

V diskusích se poměrně často objevuje otázka, zda bude 32 ROP jednotek pro čip dostačujících, zvlášť když jich 32 nese například i mainstreamový čip Barts (HD 6800). AMD před časem otevřeně přiznala, že návrhu čipu Barts předcházela simulace, jejímž cílem bylo zjistit, zda by bylo výhodnější využít plochu čipu kombinací 16 ROP s vyšším množstvím výpočetních jednotek nebo 32 ROP a méně výpočetními jednotkami. Výsledky obou možných konfigurací se lišily zanedbatelnými dvěma procenty, takže AMD zvolila pro implementaci rychlejší kombinaci se 32 ROP (zřejmě vyšla z návrhu čipu Cypress, jehož části nahradila bloky řadiče čipu Redwood). Prakticky to znamená, že i čip jako je Barts by 16 ROP neomezovalo a důvod přítomnosti 32 jednotek nesouvisí s výkonem. Pokud tedy pro čip se zhruba polovičním teoretickým výpočetním potenciálem stačí 16, je pro dvojnásobné řešení 32 optimum.

Základní koncept ROP jednotek se nezměnil od doby vydání Radeonu HD 4800 (RV770): Jednotky jsou uskupeny po čtyřech, respektive jde o čtveřici color ROP (pro práci s barvou) a 16 Z-jednotek. Dá se říct, že jednotky stále nabízejí 4× rychlejší Z/Stencil než práci s barvou a nadále 4 MSAA vzorky v taktu. AMD je v posledních letech na informace ohledně změn v architektuře ROP velice skoupá, přesto k úpravám dochází.

U řad Radeonů HD 4000 - 6000 odpovídal počet ROP celočíselnému násobku počtu paměťových kanálů a bloků L2 cache

(GPU Barts / Radeon HD 6800)

Konkrétně při přechodu z čipu RV770 na Cypress (HD 5800) vzrostla dvojnásobně kapacita color cache i Z/Stencil cache. Při vývoji Caymanu (HD 6900) došlo na podporu anti-aliasingu EQAA (nízké dopady na výkon a nízké nároky na paměť) a zrychlení FP32 operací s jedno- až dvoukanálovými daty (2× respektive 4×). Dvojnásobně byly zrychleny i operace s formátem Int16 a přibyla podpora pro sloučení zápisů, které je možné realizovat menším počtem operací.

Vzhledem k tomu, že v souvislosti s GCN (krom asociativního rozhraní) AMD žádné změny výslovně nespecifikovala, předpokládáme, že stav zůstal obdobný jako v případě výše popsaného GPU Cayman.

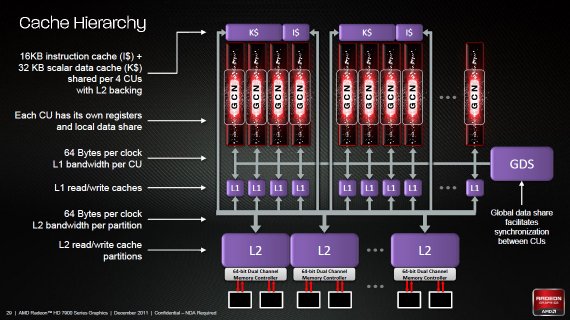

Cache

Celá struktura cache je kompletně nová záležitost a dá se říct, že po samotných výpočetních jádrech jde o nejvýraznější změnu architektury. Cache navíc nově podporují ECC (Error Checking and Correcting) bez ztráty výkonu.

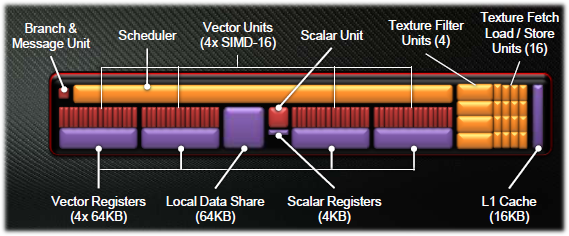

První skupina pamětí je na úrovni CU. Najdeme tu L1 cache podporující čtení i zápis, která je nově unifikovaná (slouží pro data i textury - na rozdíl od Caymanu a Fermi), podporuje komprimované textury (na rozdíl od Caymanu, ale shodně s Fermi). Na rozdíl od předešlých čipů se L1 cache sama stará o adresaci textur (dosud pro tyto účely byla v texturovacích jednotkách přítomna samostatná jednotka pro adresaci). V případě čipů Cypress a Cayman dosahovala L1 texture cache kapacity 8 KB, u Tahiti tomu bude 16 KB (dvojnásobek). Každý blok L1 je zásobován sběrnicí o přenosové kapacitě 64 bytů v taktu, takže celková datová propustnost na úrovni L1 dosahuje přibližně 1,9 TB/s.

Největší paměťový blok na úrovni CU tvoří čtveřice vektorových registrů (pro každý vec16 výpočetní blok jeden). V rámci celého čipu dosahuje jejich kapacita celých 8 MB. Obdobným registrem (ale adekvátně menším) disponuje i skalární jednotka. Poslední pamětí na úrovni CU je 64KB local data share.

Každým čtyřem CU dále slouží 16KB instrukční cache a 32KB skalárně-datová cache, které jsou připojené k L2. Naopak pro synchronizaci mezi CU jsou všechny L1 bloky připojené na společnou global data share. Jako poslední se dostáváme k již zmíněné L2, která je na většině schémat (kromě tohoto) zakreslena chybně. Ve skutečnosti se nejedná o monolitický blok, ale distribuované části, jejichž počet je závislý na počtu kanálů paměťového řadiče. Čip Tahiti v provedení Radeonu HD 7970 nese celkem 768 KB L2 cache, přičemž na každý ze 6 kanálů řadiče připadá 128 KB. Předpokládáme, že u některých modelů karet bude kapacita snížená na 64 KB na kanál, případně (a to je v podstatě jisté) bude kapacita nižší v důsledku nižšího počtu paměťových kanálů.

AMD se nepochlubilo se dvěma parametry. Jednak s kapacitou color cache a Z/Stencil cache na úrovni ROP a dále s kapacitou GDS (global data share). Druhá jmenovaná položka byla v případě čipů Cypress a Cayman rovna 64 KB, takže můžeme předpokládat, že bude na podobné úrovni (32 nebo 64 KB).

| typ | dílčí kapacita | celkem |

|---|---|---|

| L1 | 16 KB / CU | 512 KB |

| L2 | 128 KB / 64bit kanál | 768 KB |

| vec. reg. | 4× 64 KB / CU | 8192 KB |

| sc. reg. | 4 KB / CU | 128 KB |

| LDS | 64 KB / CU | 2048 KB |

| sc. data | 8 KB / CU | 256 KB |

| instr. | 4 KB / CU | 128 KB |

| GDS | 64 KB | 64 KB (?) |

| ROP | (8× Z+color cache) | ? |

| celkem | ~ 12 MB | |

I když neznáme kapacitu cache ROP jednotek (vůči ostatním číslům bude relativně zanedbatelná), můžeme říct, že čip Tahiti obsahuje celkem 12 MB paměti, což je přesně tolik, kolik měla 3Dfx Voodoo 2 v roce 1998 grafické paměti celkem :-)

AMD Tech Day, Mnichov (8. prosince)