ISSCC 2011: AMD ukazuje detailní snímky x86 jader „Llano“ a „Bulldozer“

Kapitoly článků

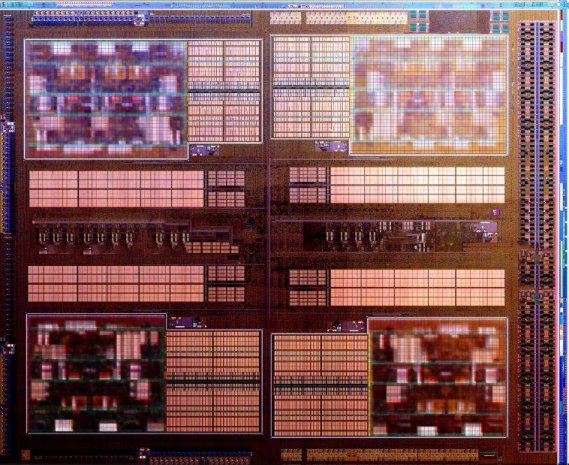

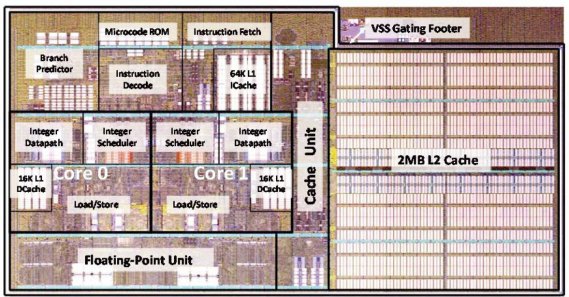

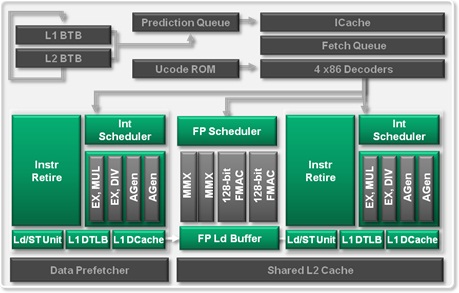

Začneme starým známým snímkem procesoru se čtyřmi „Bulldozer“ moduly, což tedy bude osmijádrový procesor. AMD skutečně kdysi jádra trochu zdeformovala, některé více rozmazala, nyní už asi nechtěla dělat drahoty a ukázala poměrně podrobné snímky jednoho Bulldozer modulu obsahujícího dvě jádra. Na „mapě“ můžete vidět, z čeho se vlastně takový „Bulldozer“ modul skládá.

Jde skutečně o zajímavou konstrukci, kde samotná x86 jádra jsou oddělena od spousty dalších věcí, které dříve bývaly jejich součástí. Především se nám tu tak trochu obloukem vrací koncept „procesor“ a „koprocesor“, zde to tedy budou dva procesory (Core 0 a Core 1), pod nimiž je onen „koprocesor“. Ten je sice jeden, ale vzhledem ke své konstrukci je schopen obsloužit požadavky obou jader. Bude-li potřeba provádět 128bit. instrukce, zvládne odbavovat obě jádra, pokud bude potřeba využít AVX (256bit. instrukce), pak bude celý tento „koprocesor“ zaměstnán a další jádro bude muset počkat.

Všimněte si také, jak je řešena L1 cache. Ta se pro každé jádro typicky dělí na instrukční a datovou, třeba u Phenomů to bylo tak, že každé jádro mělo svých 64 kB datové a 64 kB instrukční L1 cache. V „Bulldozeru“ je instrukční L1 cache o velikosti 64 kB společná pro obě jádra, datovou L1 cache má každé jádro vlastní o velikosti pouze 16 kB. Sdílená je pak tradičně L2 cache pro obě jádra, té jsou pro celý „Bulldozer“ modul 2 MB, více „Bulldozer“ modulů pak bude sdílet ještě velkou L3 cache.

| Přečtěte si také | |

|---|---|

|

AMD představuje mikroarchitektury „Bulldozer“ a „Bobcat“ |

|

AMD hovoří o sdílené FPU v Bulldozeru: „Flex FP“ |

|

AMD ukázala upravený die-shot procesoru s jádry „Bulldozer“ |

Trocha čísel: jeden „Bulldozer“ modul čítá zhruba 213 miliónů tranzistorů (celý dvoujádrový Athlon 64 jich měl 233 miliónů) a při 32nm výrobním procesu zabírá plochu 30,9 mm². Počítá se s napájecím napětím od 0,8 do 1,3 V a s takty až kolem 3,5 GHz.

Diskuse ke článku ISSCC 2011: AMD ukazuje detailní snímky x86 jader „Llano“ a „Bulldozer“