Mikrosnímek nových Epyců prozrazuje, co ukrývá centrální jádro

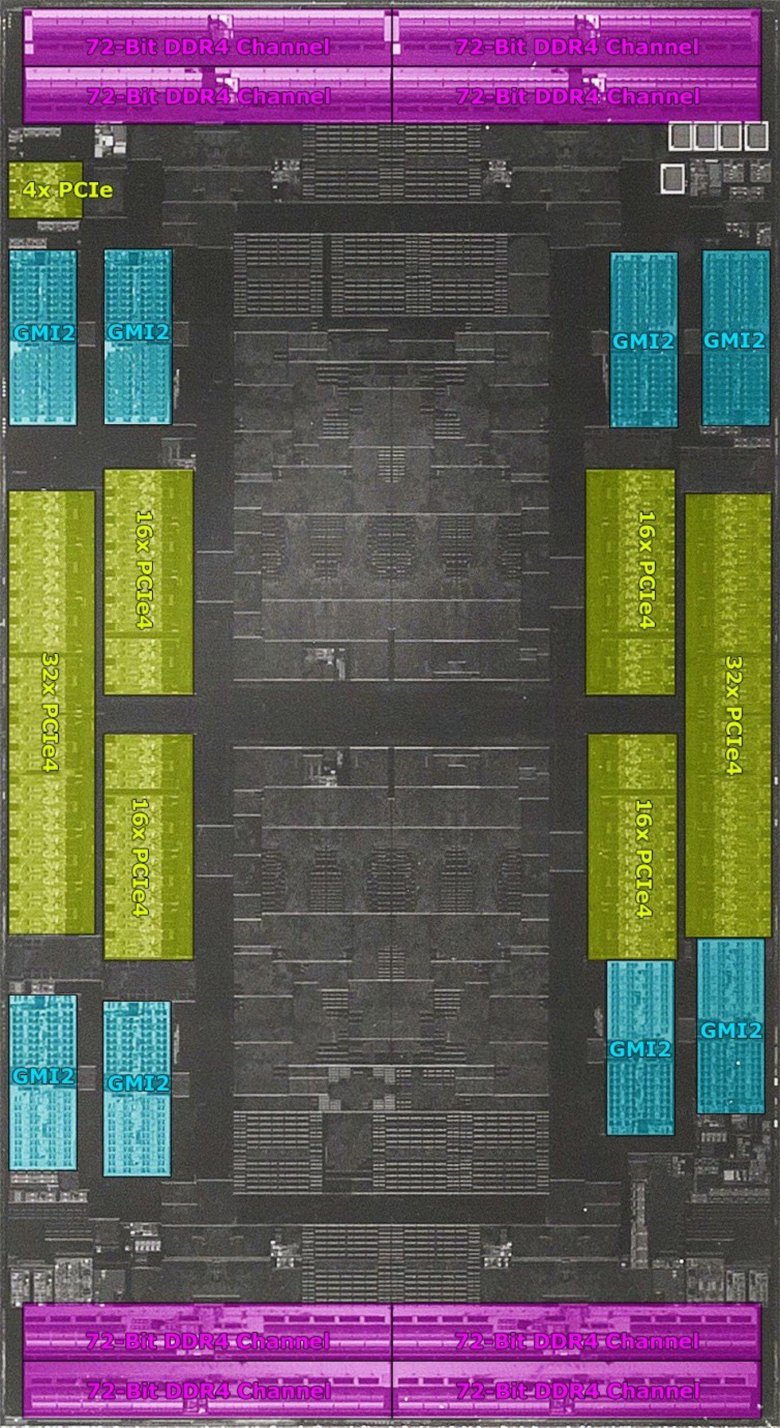

Rovnou a bez napínání si můžeme říct, že skutečně velké množství SRAM obsahuje (centrální část), ale ta se nechová (a především nehlásí) jako klasická L4 cache procesorových jader, ale patrně zajišťuje rychlou komunikaci mezi všemi typy rychlých rozhraní, kterými je jádro vybaveno. Vpravo níže vidíte barevně zvýrazněná rozhraní pro DDR4 paměti (fialová), GMI pro připojení 7nm osmijádrových Zen 2 čipletů (bledě modrá) a rozhraní PCIe 4.0 (žlutá).

Centrální část obsahuje hlavně SRAM a samotné řadiče (nebo jak krásně Google translator překládá z německého článku webu HardwareLuxx, který snímky pořízené uživatelem Locuza pustil do světa, „přepínače příčníků“).

| Zen | Zen 2 | |||

|---|---|---|---|---|

| ↓ komponenty ↓ | plocha | tranzistory | plocha | tranzistory |

| 1xnm modul Zeppelin | 212 mm² | 4,8 mld. | - | - |

| 7nm čiplet | - | - | 74 mm² | 3,9 mld. |

| 1xnm IO čiplet (Ryzen) | - | - | 125 mm² | 2,09 mld. |

| 1xnm IO čiplet (Epyc) | - | - | 416 mm² | 8,34 mld. |

| ↓ produkty ↓ | ||||

| Ryzen 1000 / 2000 | 212 mm² | 4,8 mld. | - | - |

| Ryzen 3000 6-8 jader | - | - | 199 mm² | 5,99 mld. |

| Ryzen 3000 12-16 jader | - | - | 273 mm² | 9,89 mld. |

| Epyc (Naples / 1. gen.) | 848 mm² | 19,2 mld. | - | - |

| Epyc (Rome / 2. gen.) | - | - | 1008 mm² | 39,54 mld. |

Tabulka sumarizuje (sice) již známé údaje, ale v kontextu snímků dobře ilustruje, že u 16jádrových Ryzenů a 64jádrových Epyců mezigeneračně téměř nevzrostl počet tranzistorů přepočtený na jedno procesorové jádro, takže architektonická vylepšení v kombinaci s čipletovou režií prakticky nezvýšila počet tranzistorů při implementaci těchto prvků.