Milan-X s V-cache je v pěti testech maximálně o 7,6 % rychlejší než Milan

Redakce webu Chips and Cheese připravila článek zaměřený na měření latencí a datové propustnosti serverových procesorů Epyc Milan-X s V-cache. Jen okrajově (pěticí měření) se věnovala výslednému celkovému výkonu. Z těchto pěti testů je Milan-X v jednom případě o 1,6 % pomalejší než Milan. V ostatních je rychlejší: O 1,4 %, 4,6 %, 4,9 % a 7,6 %.

Proč je v jednom testu pomalejší? V-cache má sice velmi vysokou datovou propustnost, ale oproti standardní L3 cache zvyšuje latenci. Pokud je trojnásobná kapacita pro konkrétní aplikaci menším přínosem než vyšší latence, pak může být výkon nižší. Test potvrzuje, že tento scénář není (v rámci pětice úloh) obvyklá situace. Na druhé straně v rámci této pětice není aplikace, která by z vyšší kapacity nějak výrazněji profitovala.

Nárůsty na úrovni desítek procent se tak skutečně týkají jen specifických úloh, pro které jsou procesory s konvenční kapacitu L3 cache limitující. To jsme však očekávali (pokud by zvýšení kapacity cache mělo přinést v širší míře závratné posuny výkonu, dávno by cache procesorů dosahovala násobných kapacit).

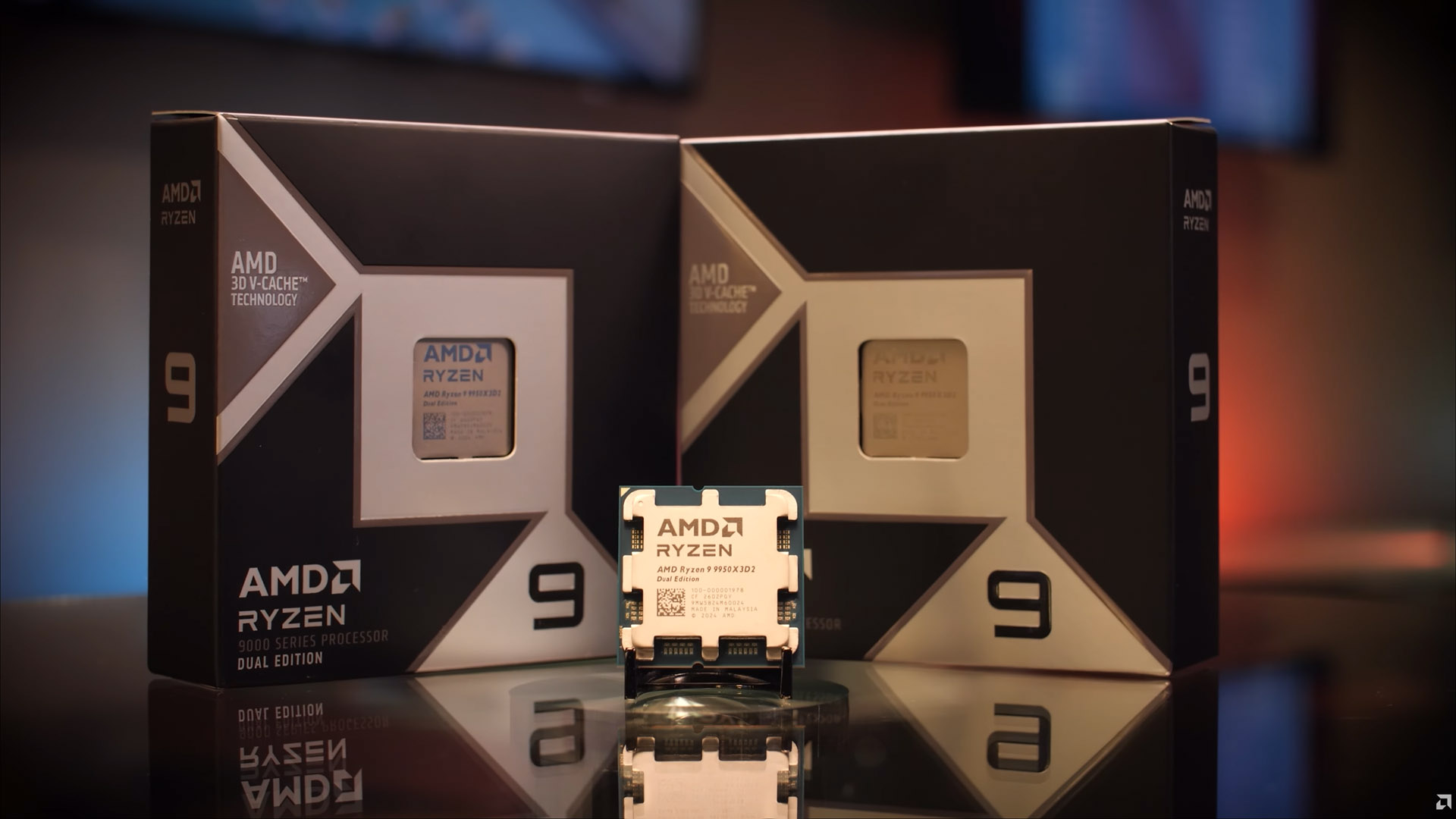

Tyto výsledky rovněž potvrzují, že pro desktop nemá Ryzen 5000 s V-cache smysl v jiné než herní konfiguraci, takže by dvanáctijádrové a šestnáctijádrové modely neměly valný smysl. Zdůraznění této generace má skutečně smysl, neboť do budoucna se mohou objevit procesory, které budou mít L3 cache kompletně přesunutou na úroveň samostatné vrstvy. První takovým případem nejspíš bude Epyc Bergamo. Lze očekávat, že by podobným způsobem mohla AMD V-cache implementovat i některým APU, u nichž by sloužila jako tzv. SLC, System-Level Cache, dostupná procesorovým i grafickým jádrům. Tato „rozšířená Infinity Cache“ by citelně snížila závislost integrované grafiky na systémových pamětech, čímž by bylo možné dosahovat mezigeneračních posunů výkonu i v situacích, když by systémové paměti mezigeneračně nepřinášely žádný podstatný posun datové propustnosti, ale výrobní proces by dovoloval implementaci výkonnějšího grafického jádra. Za předpokladu dostatečně rychlých linek GMI by se u čipletových produktů mohla taková SLC nacházet na centrálním čipletu, který generuje minimum odpadního tepla a neomezovat výkon grafických a procesorových jader.