Nehalem klepe na dveře

Kapitoly článků

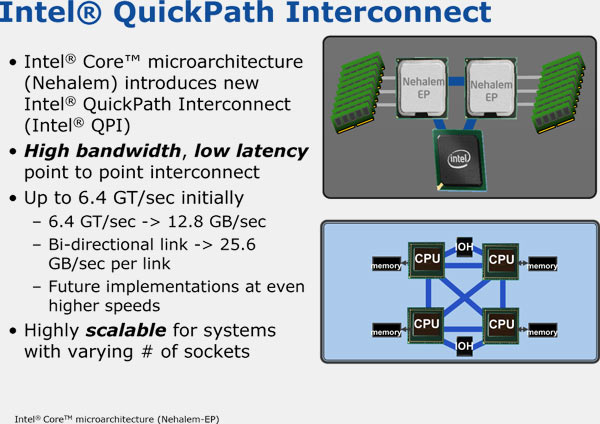

Mikroarchitektura „Nehalem“ jako taková je o několika základních věcech. V první řadě dává vale starému způsobu komunikace mezi procesorem a čipsetem známým jako Front Side Bus. Se zkratkou FSB se však budeme setkávat i nadále, minimálně pojem „sběrnice“ bude stále hrát svou roli (pořád je v Core i7 jakási základní frekvence, zde 133 MHz, od níž se s pomocí násobiče odvíjí skutečná rychlost procesoru), přestože komunikační rozhraní, skrze které si procesory postavené na mikroarchitektuře „Nehalem“ povídají s čipsetem, už se sběrnicí nazývat nedá. Nové procesory, které budou zanedlouho uvedeny pod již oficiálně známým označením „Core i7“, komunikují s čipsetem pomocí nového QuickPath Interconnect rozhraní (zkráceně QPI), jehož podobnost s otevřeným HyperTransportem, které používají procesory AMD od mikroarchitektury K8 dále, není až tak docela čistě náhodná. Minimálně odtud Intel vzal inspiraci. Musel, protože s pomalou FSB by si dlouho nevystačil (vše se dohánělo od dob „Core“ velkou cache a jinak poměrně vydařenou mikroarchitekturou, která dala základ tomu, čemu se dnes říká „Nehalem“ – ve skutečnosti Intel jiné jméno pro tuto mikroarchitekturu nemá, té současné říká Core „Merom“ a této nové Core „Nehalem“). A tak, zatímco dnešní FSB dokázala dosáhnout na nějakých 1 600 MHz, což efektivně znamená tentýž počet přenosů za sekundu, v případě jednoho QPI spoje můžeme klidně hovořit od začátku o rychlosti 6,4 GT/s a reálné propustnosti 12,8 GB/s v jednom směru (obousměrně pak 25,6 GB/s, představit si to můžete jako full-duplexní 100Mbitový ethernet, kde se tím pádem v obou směrech současně dá přenášet dohromady 200 Mbit/s). Obdobně jako u AMD, procesory Core i7 mohou mít v serverové podobě více QPI linků a komunikovat nejen s čipsetem, ale i navzájem přímo mezi sebou, případně s jinými čipy, které budou mít QPI rozhraní.

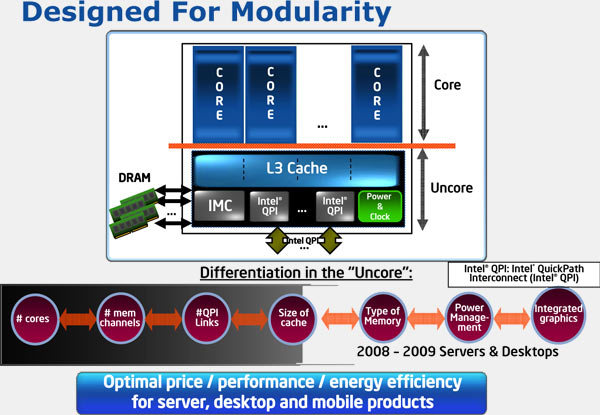

Druhým základním stavebním kamenem nových procesorů, který jakoby opět bral inspiraci u konkurence, je integrace paměťového řadiče přímo do procesoru. Tím se nám procesory Intel začínají dělit na dvě základní části: „Core“ a „Uncore“. Do Core patří základy CPU, tedy samotná jádra s L1 a L2 cache. L3 cache spolu s dalšími částmi, jako je paměťový řadič, rozhraní QPI a řízení taktu a napájení jednotlivých částí celého procesoru, to vše už patří do „Uncore“

Samotný paměťový řadič již zcela opouští dnes stále ještě nejrozšířenější DDR2 paměti a vsází vše na DDR3 a aby to bylo atraktivnější než u konkurence, řadič je tříkanálový. Teoretická maximální propustnost je 25,5 GB/s, v praxi to bude samozřejmě o něco méně.