Tajnou zbraní Intel Meteor Lake má být až 512MB Adamantine Cache

Pokud jde o cache a Intel, lze v historii najít několik zajímavých řešení - žádné z nich se však nedokázalo prosadit a od každého bylo velmi brzy upuštěno.

Intel Broadwell Iris Pro s eDRAM

Vzpomenout můžeme na tzv. Crystal Well, což byla L4 cache implementovaná prostřednictvím eDRAM v procesorech Broadwell, kde dosahovala až 128MB kapacity. V omezené míře (jen na vybraných mobilních modelech) se objevila ještě u generace Skylake, ale pak v tichosti vyšuměla (Intelu se s její pomocí podařilo ±dorovnat integrované grafiky APU od AMD, ovšem u čipů s několikanásobně vyšší cenou, což příliš nefungovalo).

Intel Knights Landing s MCDRAM / HMC

Dalším příkladem může být o posledních generacích derivátů Larrabee, výpočetních akcelerátorů Xeon Phi, které Intel osadil HMC pamětmi od Micronu. Ty bylo možné používat jako standardní operační paměť, ale mohly běžet v režimu jakési improvizované cache na úrovni mezi RAM a cache procesorových jader. Problém byl, že v režimu cache výrazně narůstaly latence pro mis (tedy pokud data nebyla v cache nalezena), nemluvě o neúspěchu samotných HMC pamětí i akcelerátorů Xeon Phi.

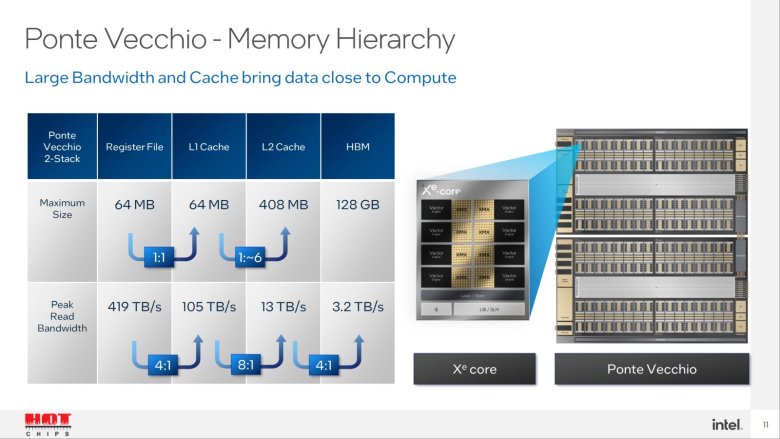

Třetím příkladem, který je skutečně soudobý, byť se jej Intelu dlouhodobě nedaří dostat na trh, jsou akcelerátory Xe-HPC alias Ponte Vecchio, alias dlaždicové řešení pro superpočítač Aurora. Toto puzzle (tvořené 63 křemíkovými dílky vyráběnými 5 různými procesy ve 24vrstvém pouzdru) Intel aktuálně řeší, byť asi ne plně úspěšně, neboť jeden ze dvou vydaných modelů „odvydal“ a po druhém stále není ani vidu ani slechu. Pro dnešní kontext je podstatné, že jedna z typu dlaždic (10nm), nazvaná Rambo Cache a umístěná až v počtu osmi kusů v ose procesoru, poskytuje akcelerátoru až 408 MB L2 cache v podobě SRAM. V roce 2019, kdy Intel o Rambo Cache oficiálně promluvil, byla 408MB nepředstavitelná kapacita - v důsledku zpoždění se však z tohoto čísla v HPC segmentu stává vcelku běžná hodnota (standardní Epyc Genoa disponuje 384 MB L3 cache a procesor Genoa-X, jehož vydání AMD chystá zhruba na letošní pololetí, bude vybaven 1152 MB L3 cache).

Adamantine cache pro Meteor Lake a Battlemage

Nějakou dobu se objevují informace o tom, že Meteor Lake bude vybaven novou cache, nicméně zdroje si až doposud výrazně odporovaly. Podle některých měla být přístupná výhradně pro procesorová jádra, podle další pro grafická jádra, přitom cache čtvrté úrovně dávala smysl převážně tehdy, pokud by byla přístupná pro obojí (přičemž už cache třetí úrovně tradičně Intel koncipoval jako přístupnou CPU i GPU, takže by oddělení pro L4 nedávalo valný smysl).

| Next generation client SoC architectures may introduce large on-package caches, which will allow novel usages. Access time for the L4 (e.g., "Adamantine" or "ADM") cache may be much less than the DRAM access time, which is used to improve host CPU and security controller communications. Embodiments help to protect innovations in boot optimization. |

Výše uvedená citace pochází z patentu Intelu z roku 2021, která cache označuje jako Adamantine, zkráceně ADM a specifikuje, že jde o L4 na bázi SRAM. Má být mj. implementovaná tak, aby se využívala teprve po nabootování systému a (o desítky sekund) neprodlužovala najetí systému. Patent hovoří pouze o využití ze strany CPU, nicméně podle kontaktu, který má YouTube kanál MLID u Intelu, bude sloužit jak procesorovým tak grafickým jádrům.

Cache byla připravena pro procesory Meteor Lake a grafické čipy Battlemage. Intel aktuálně testuje (pro Meteor Lake) kapacity 128-512 MB.

Nebylo by překvapivé, pokud by Intel procesorům s výkonnější integrovanou grafikou doplnil nějaké desítky MB cache. Nicméně kapacity ve stovkách MB (tedy i násobně více než mají top modely velkých GPU jako Lovelace AD102 nebo Navi 31) přinášejí otázku, co s nimi vlastně bude čip dělat a k čemu by mu v praxi mohly pomoci. Nároky SRAM na křemík totiž opravňují vznik obavy, zda takové řešení produkt neprodraží více než o kolik navýší jeho výkon (což byl i problém Broadwellu nehledě na použití levnější eDRAM). Možná však jen dostupné zdroje nedisponují všemi potřebnými informacemi a Adamantine nebude cache integrovaná společně s dalšími obvody, ale půjde o vrstvení, podobně jako používá AMD, nebo jinou technologii, která umožní předejít přílišnému růstu nákladů (z hlediska nákladů by mohla dávat smysl integrace do podložky - interposer - na které jsou dlaždice umístěné).

Navzdory tomu zůstává otázka, čemu by v mobilním prostoru mohla pomoci takto velká cache. Procesorová jádra mají zůstat v konfiguraci maximálně 6 + 8, takže se (oproti současným až 8 + 16) rozhodně nečeká velký nárůst procesorového výkonu, kterému by nestačila rychlost systémové paměti. Grafické jádro sice Intel plánuje mezigeneračně zrychlit cca 2×, ale i kdyby se tím v kombinaci s použití velké cache dostal na výkon o pár procent vyšší než AMD Phoenix, bude to s ohledem na výrobní náklady takového řešení spíše vítězství Pyrrhovo (viz Broadwell). Nakonec zvýšení herního výkonu, ke kterému AMD v desktopových procesorech využívá V-cache, nedává v případě úsporné řady mobilních procesorů Intel valný smysl (tam nelze očekávat párovnání se samostatnou grafikou, která by byla výkonem procesoru omezena).

Bude tedy velmi zajímavé sledovat, jak Intel situaci vyřeší technologicky, i jak se s ní vypořádá marketingově, neboť segmenty, do kterých Meteor Lake prozatím míří, se požadavky na velkou cache až doposud příliš nevyznačovaly.