Z NAND Flash se stávají mrakodrapy, Toshiba chystá 128patrový

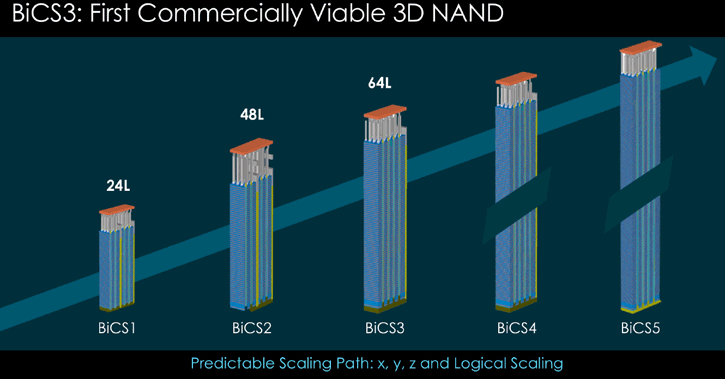

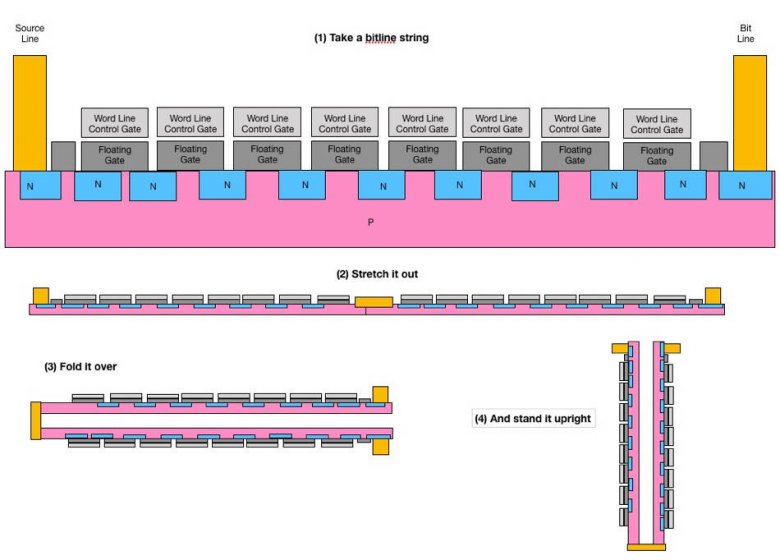

Toshiba dokončuje implementaci generace, které říká BiCS-5. Tu lze stručně charakterizovat jako 128vrstvou generaci 3D NAND Flash. BiCS-4 je 96vrstvá, BiCS-3 je 64vrstvá. Plošné rozměry pouzdra se nemění, jen mírně stoupne jeho výška.

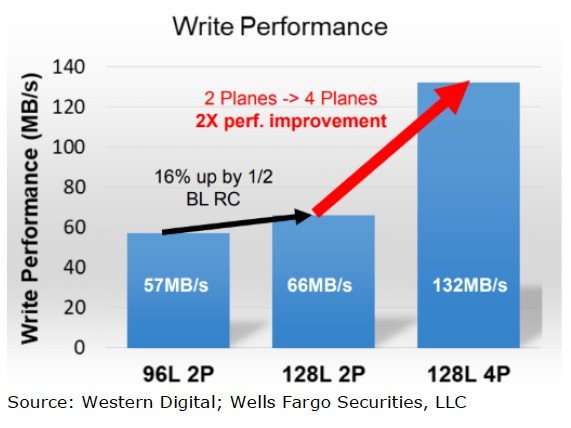

BiCS-5 však nepřináší jen zvýšení počtu vrstev, jak by se na první pohled mohlo zdát. Implementuje totiž tzv. 4-plane design oproti stávajícím (např. BiCS-4) se 2-plane desing. Co to znamená: Každé křemíkové jádro je rozděleno na čtyři samostatně fungující části (namísto dvou), k nimž lze přistupovat separátně. Protože lze zapisovat paralelně, znamená to zdvojnásobení rychlosti zápisu ze 66 na 132 MB/s.

Další technologickou změnou je implementace tzv. CuA, což znamená Circuity Under Array, kdy je řídící logika přesunuta do samostatné spodní (nejnižší) vrstvy. Tím dochází l úspoře ~15 % křemíku ve srovnání s klasickým konceptem.

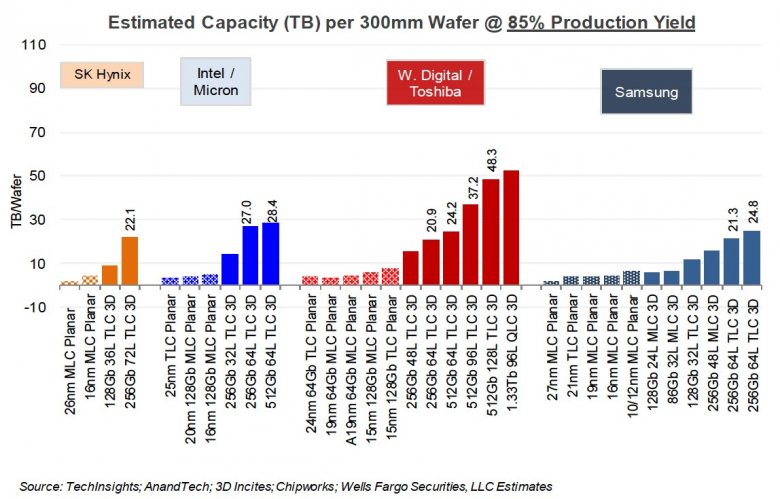

V čem je tato první generace 128vrtstvcýh 3D NAND Flash spíše konzervativní, je konfigurace buněk. Využívá 3bit buňky (cells), tedy TLC, nikoli 4bit (QLC). Důvodem je velmi pravděpodobně (prakticky zcela jistě) nedořešená nižší výtěžnost QLC, v jejímž důsledku lze podle projekcí některých analytiků ze stejného množství křemíku vyrobit TLC i QLC o prakticky stejné výsledné datové kapacitě. Tím QLC nepřináší téměř žádnou výhodu (z hlediska poměrů výrobní náklady / možná prodejní cena), což zároveň může být důvodem, proč Toshiba přišla se 128vrstvými BiCS-5, které poslouží jako dočasný suplent QLC, než se podaří výtěžnost doladit.

Očekává se, že by 128vrstvé BiCS-5 mohly být na trhu již v roce 2020, nejdéle pak v první půlce roku 2021.