Zen 5 (Nirvana): 6 ALU + 80kB L1 cache potvrzeny, Zen 6 (Morpheus) v roce 2025

Zen 5 / Nirvana

Zen 5, o kterém se toho dozvídáme nejvíc, je architekturou, která v první implementaci půjde na trh zhruba koncem jara příštího roku. Jako první dojde na desktopovou variantu pro socket AM5, později přijdou mobilní APU a serverové modely.

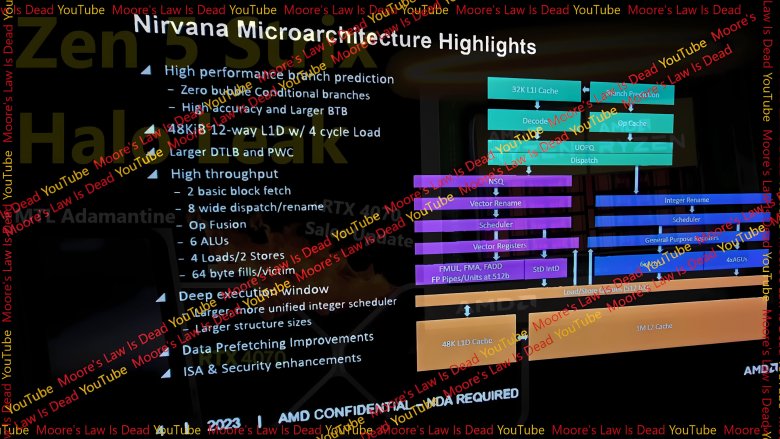

Diagram Zen 5 (MLID)

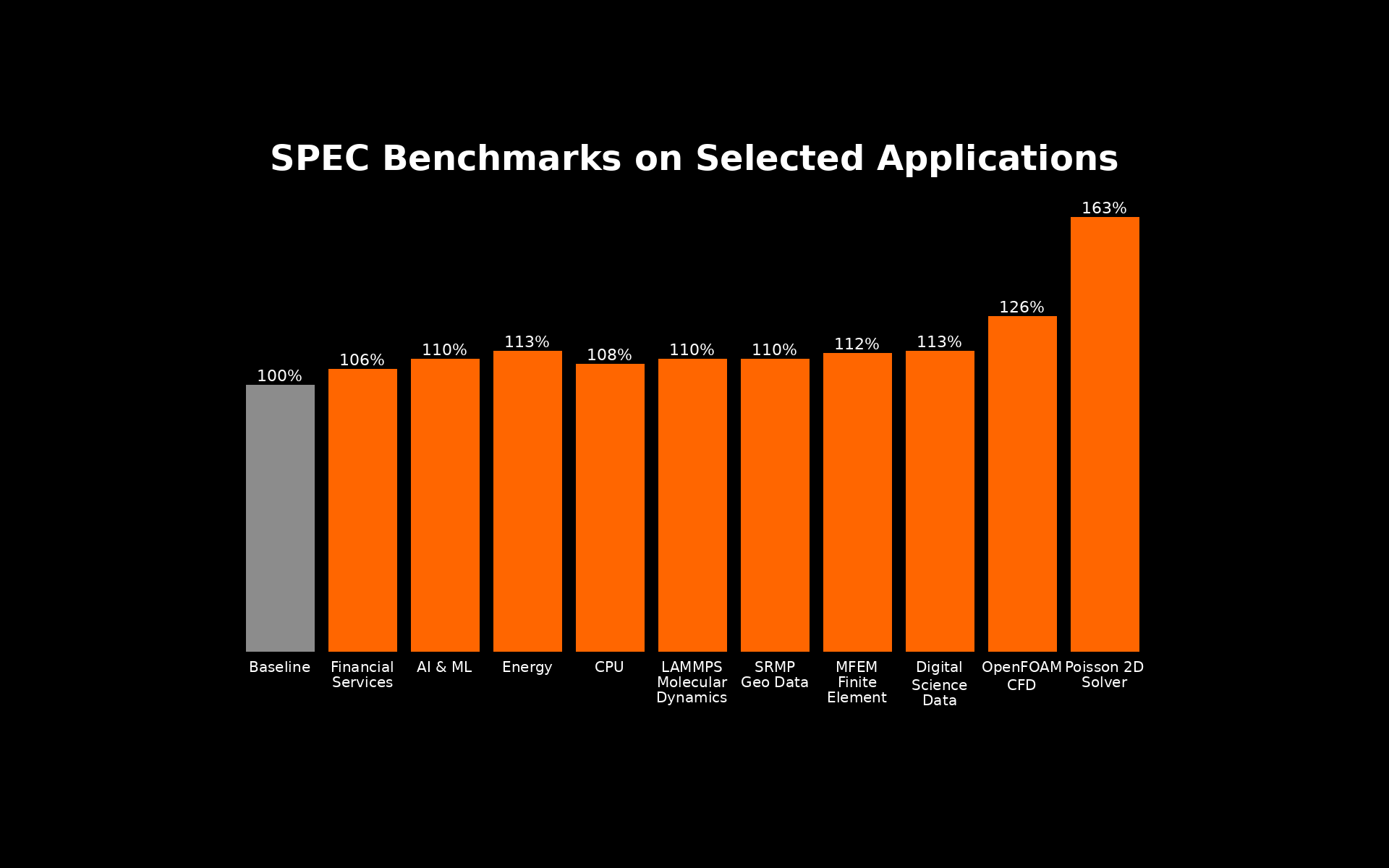

Slajd potvrzuje zvěsti o rozšíření 64kB L1 cache na 80 kB (datová část se zvětší na 48 kB) a rovněž je zmíněn nárůst DTLB. Front-end byl rozšířen z podpory šesti operací (za cyklus) na osm a samotné jádro z konfigurace kombinující 4 ALU + 3 AGU u Zen 4 narostlo na 6 ALU + 4 AGU u Zen 5, což je největší mezigenerační nárůst v dosavadní historii Zenu.

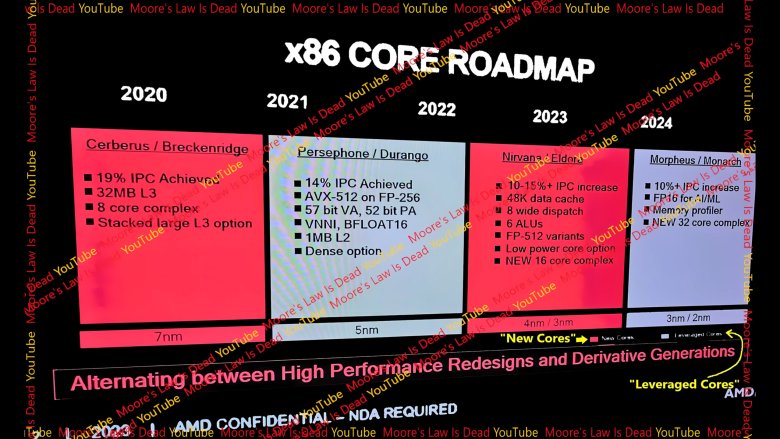

AMD Zen roadmapa (MLID)

Z roadmapy architektury Zen se dále dozvídáme, bude existovat varianta jádra Zen 5 s plnou 512bit šířkou (pro zpracování AVX-512 v jednom průchodu), což znamená, že bude existovat i verze se stávající 256bit šířkou, kde je AVX-512 zpracováváno obdobně jako na Zen 4. Poznámce „new 16 core complex“ je potřeba rozumět tak, že u Zen 4 i v podobě šestnáctijádrové (Zen 4c) dlaždice použité na serverových procesorech Bergamo byla v křemíku přítomna dvojice osmijádrových CCX (core complex). Se Zen 5 se maximální konfigurace CCX rozšíří z osmi jader na šestnáct, což rozšíří efektivních využitelnost těchto čipletů i na další typy zátěže (zejména takové, kdy všech šestnáct jader spolupracuje na jedné úloze a je žádoucí sdílení stejných data pro všechna tato jádra v rámci L3 cache).

Samostatný odstavec si zaslouží vysvětlení, jak se orientovat ve výše zobrazeném slajdu (roadmapě). Jde o interní dokument, takže orientace v něm není příliš intuitivní. Roky (nahoře) nejsou umístěné na začátku roku, ale v jeho polovině a vydání konkrétní architektury odpovídá pravému okraji chlívečku. Neméně intuitivní je vyčíslení IPC. Zatímco u vydaných produktů je uvedeno reálně dosažené IPC (xy% IPC achieved), u chystaných jde pouze o projekci. Zda to chápat jako konzervativní výhled nebo údaje pro matení konkurence, nechám na vás, ale připomeňme, že již u minulých generací Zenu uváděla AMD podstatně nižší hodnoty, než jakých následně dosáhla. Například pro Zen (1) to bylo „až 40 %“, zatímco nakonec šlo o „minimálně 52 %“ a pro Zen 4 to bylo „8 %“, ze kterých se nakonec stalo 14 %. Z hodnot „10-15 %+“ pro Zen 5 a „10 %+“ pro Zen 6 se tak dozvídáme pouze (již známou) informaci, že nárůst IPC u Zen 6 bude nižší než u Zen 5.

Zen 6

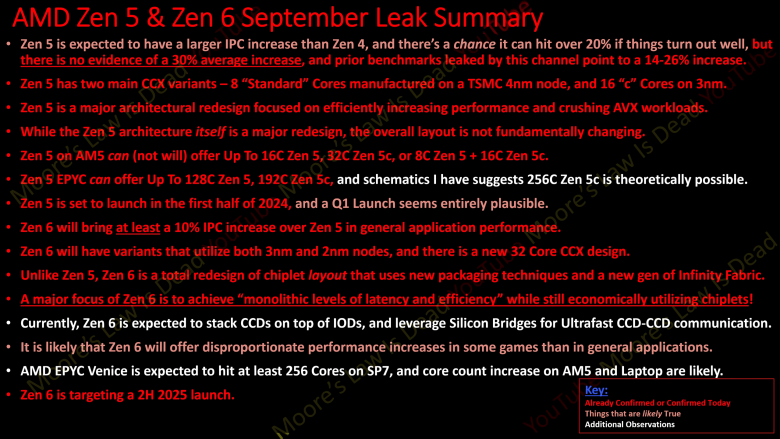

Tím se dostáváme k Zen 6. Zatímco doposud to vypadalo, že k vydání této generace dojde někdy v zimě 2025 / 2026, z interních dokumentů AMD vyplývá, že by tuto architekturu ráda poslala do světa ještě před koncem roku 2025.

Jak už je známo, nárůst IPC bude nižší než u Zen 5 (což je u sudých verzí, které ladí architekturu lichých verzí, obvyklé), což bude kompenzováno novějším výrobním procesem v kombinaci se zvýšeným počtem jader. MLID potvrzuje zprávy RedGamingTech, že AMD uvažuje o navrstvení procesorového čipletu (CCD) na centrální čiplet (IOD). To by podstatně snížilo latence mezi jádry v různých čipletech. Zároveň bude existovat až 32jádrový komplex (CCD), který patrně najde uplatnění v serverové variantě Zen 6c.

Přestože Zen 6 rozvíjí x86 architekturu Zen 5, je kombinace přechodu na 3nm+2nm procesy společně se změnou v architektuře čipletů a organizací CCX hodně velký a tedy i riskantní krok. Pokud se toto AMD skutečně povede uzavřít a dostat na trh před koncem roku 2025 (tedy zhruba do dvou let), pak klobouk dolů.