Zen 6 APU Medusa Point v Geekbench: hlásí 32MB L3 cache

Víme, že Zen 6 zůstane u 1MB L2 cache na každé jádro. x86 jádrům AMD z nějakého důvodu tato kapacita stačí a nabízejí s ní výkon konkurenceschopný x86 jádrům Intelu s 3MB L2 cache na jádro (u některých mobilních modelů sníženou na 2MB L2 cache na jádro). U AMD se chystá změna se Zen 7 (2MB L2 cache na jádro) a rovněž Intel již seznal, že nemůže kapacitu této cache navyšovat tak strmě a s Nova Lake dojde ke kompromisu (více v odkazu níže), ale to jen pro úplnost.

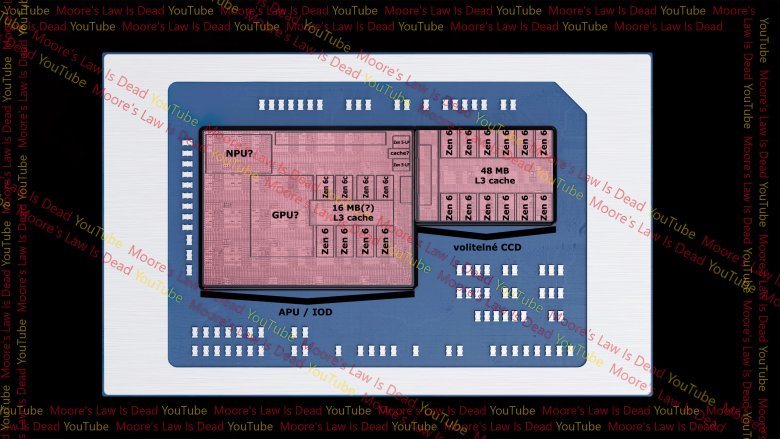

Co se u procesorů na architektuře Zen 6 může změnit a změní, je kapacita L3 cache. V klasických čipletech vzroste z 32MB na 48MB (kapacita na jádro zůstane zachovaná, ale při vytížení nižšího počtu jader či vláken efektivně vzroste). Složitější je situace v mobilním segmentu, ve světě APU. Tam je základem Medusa Point, řešení integrující všechny základní obvody od CPU a GPU jader až po řadič, ke kterému bude možné volitelně doplňovat čiplety zvyšující procesorový výkon (+12 jader Zen 6 se 48MB L3 cache) nebo grafický výkon (RDNA 5 GPU).

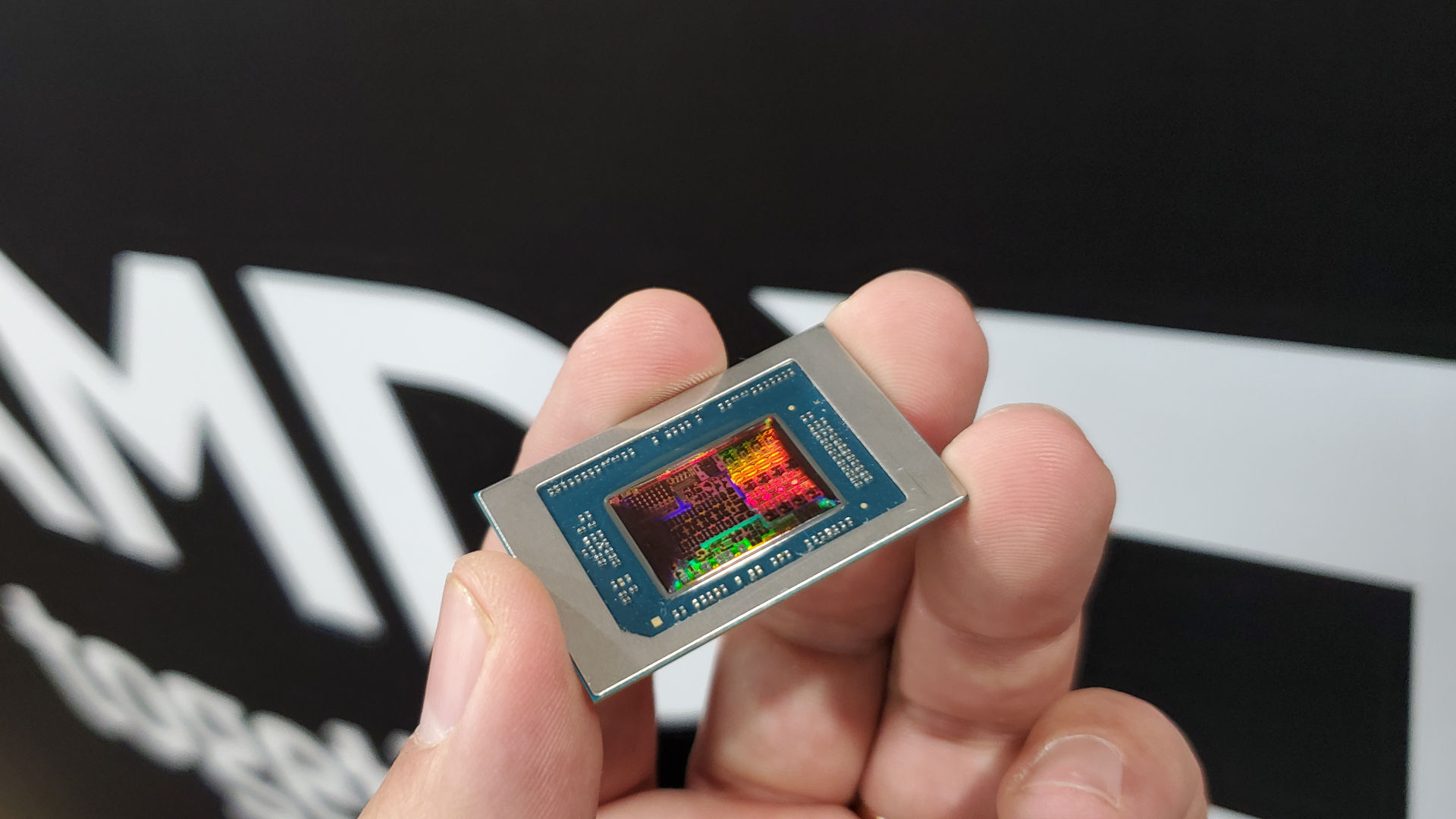

APU Medusa Point (Geekbench)

Základní Medusa Point ponese 4 jádra Zen 6, 4 jádra Zen 6c a 2 úsporná jádra Zen-LP. Celkem tedy 10 jader. To ostatně hlásí i Geekbench 6. Rovněž však hlásí 32MB L3 cache, což by byl nečekaný posun. Komplex osmi hlavních jader má totiž podle doposud dostupného schématu nést L3 cache, která je ve srovnání se známou 48MB L3 cache dvanáctijádrového čipletu méně než poloviční.*

*znázorněna je poloviční plochou, přičemž by její denzita měla být s ohledem na ~3nm proces nižší než denzita L3 cache ve ~2nm čipletu.

To by při obvyklých krocích odpovídalo 16MB, nicméně Geekbench mluví o 32MB. Někde tedy něco nesedí.

APU Medusa Point s volitelným 12jádrovým čipletem (podklad MLID, popisky DIIT)

Pokud bychom hledali místo možného rozporu nebo chyby, je problémem, že může být jak na straně Geekbench, tak na straně dostupného schématu. Geekbench totiž pracuje s CPUID, hlášením OS i firmwarem (nezjišťuje kapacitu přímo testováním hardwaru) a u nevydaných produktů může být chyba prakticky na všech zmíněných úrovních. Na druhé straně, nepřesný může být i nákres. Pokud bychom vycházeli striktně z něj a známého faktu, že dvanáctijádrový čiplet nese 48MB, přičemž u centrálního čipletu musí být denzita nižší (3nm vs. 2nm), pak se dostáváme na kapacitu 20-21MB, což je dost daleko od hlášených 32MB L3.

V tomto ohledu se nejspíš dočkáme ještě nějakého překvapení.

Záznam z Geekbench sice ukazuje i konkrétní výkonnostní výstup, ale ten je zkreslen omezením taktu procesorových jader na 2 GHz. To je v průměru zhruba polovina toho, jakých taktů v této vícevláknové zátěži dosahuje současný Strix Point. Kdybychom výsledek prachsprostě zdvojnásobili, dostáváme se s konfigurací 4× Zen 6 + 4× Zen 6c + 2× Zen-LP zhruba na 14600 bodů, což plus mínus odpovídá skóre, které dosahuje Ryzen AI 9 HX 370 / Strix Point / 4× Zen 5 + 8× Zen 5c.

Což odpovídá našemu očekávání (viz výše).