AMD chystá gigantické výpočetní APU: Instinct MI300 ze 4 GCD s připojenými CCD

Loni v listopadu vydala AMD Instinct MI100 s jádrem Arcturus, od letošního jara mají partneři společnosti v rukou Instinct MI200 s jádrem Aldebaran (formální vydání proběhne opět koncem roku) a někdy na rok 2022-2023 (různé zdroje mají různé názory) chystá AMD Instinct MI300, který ponese jádro Rigel.

Podle leakera ExecutableFix se připravuje serverový socket SH5, který bude možné osadit zařízením s CPUID 0xA80F00. To odpovídá akcelerátoru Instinct MI300, o němž jsme informovali v první polovině září.

| AMD Radeon Instinct MI60 | Instinct MI100 | Instinct MI200 | Instinct MI300 | Nvidia A100 | |

|---|---|---|---|---|---|

| GPU | Vega 20 | Arcturus | Aldebaran | Rigel | GA100 |

| architektura | GCN4 | CDNA | CDNA2 | CDNA3 | Ampere |

| CPU | |||||

| formát | PCIe | PCIe | OAM | OAM | SXM4 / PCIe |

| CU/SM | 60 | 120 | 240 (256) | (384-512?) | 108 |

| FP32 jader | 3840 | 7680 | 15360 (16384) | (24k-33k?) | 6912 |

| FP64 jader | - | - | - | - | 3456 |

| INT32 jader | - | - | - | - | 6912 |

| Tens. Cores | - | ? | ? | ? | 432 |

| takt | 1800 MHz | 1502 MHz | ≤1500 MHz | ? | 1410 MHz |

| ↓↓↓ T(FL)OPS ↓↓↓ | |||||

| FP16 | 29,5 | 184,6 | 369 | ? | 78 |

| BF16 | 92,3 | 185 | ? | 39 | |

| FP32 | 14,7 | 23,5 | 92,3 | ? | 19,5 |

| FP64 | 7,4 | 11,5 | 46,1 | ? | 9,7 |

| INT4 | 118 | 184,6 | ? | ? | ? |

| INT8 | 59,0 | 184,6 | ? | ? | ? |

| INT16 | 29,5 | ? | ? | ? | ? |

| INT32 | ? | ? | ? | ? | 19,5 |

| FP16 tensor | 184,6 | 369 | ? | 312/624* | |

| BF16 tensor | 92,3 | 369 | ? | 312/624* | |

| FP32 tensor | 46,1 | 92,3 | ? | 19,5 | |

| TF32 tensor | ? | 156/312* | |||

| FP64 tensor | 46,1? | ? | 19,5 | ||

| INT8 tensor | 184,6 | 369 | ? | 624/1248* | |

| INT4 tensor | ? | 1248/2496* | |||

| ↑↑↑ T(FL)OPS ↑↑↑ | |||||

| TMU | 240 | 480? | 960? (1024)? | ? | 432 |

| sběrnice | 4096bit | 4096bit | 8192bit | ? | 5120bit |

| kapacita paměti | 32 GB | 32 GB | ≤128 GB | ? | 40 GB 80 GB |

| HBM2 | 2,0 GHz | 2,4 GHz | 3,2 GHz | HBM3? | 2,43 GHz 3,20 GHz |

| paměť. propustn. | 1024 GB/s | 1229 GB/s | 3277 GB/s | ? | 1555 GB/s 2048 GB/s |

| TDP | 300 W | 300 W | ≤600W? | ~600W? | 400 / 250 W |

| transistorů | 13,2 mld. | 50,0 mld. | >100 mld.? | ? | 54,2 mld. |

| plocha GPU | 331 mm² | 750 mm² | ? | ? | 826 mm² |

| proces | 7 nm | 7 nm | ? | ? | 7 nm |

| datum | 2018 | 2020 | 2021 | 2022-2023 | 2020 |

*pouze při využití sparsity / Sparse Tensor Cores

Tabulka obsahuje údaje o nevydaných produktech, které nejsou oficiálně potvrzené

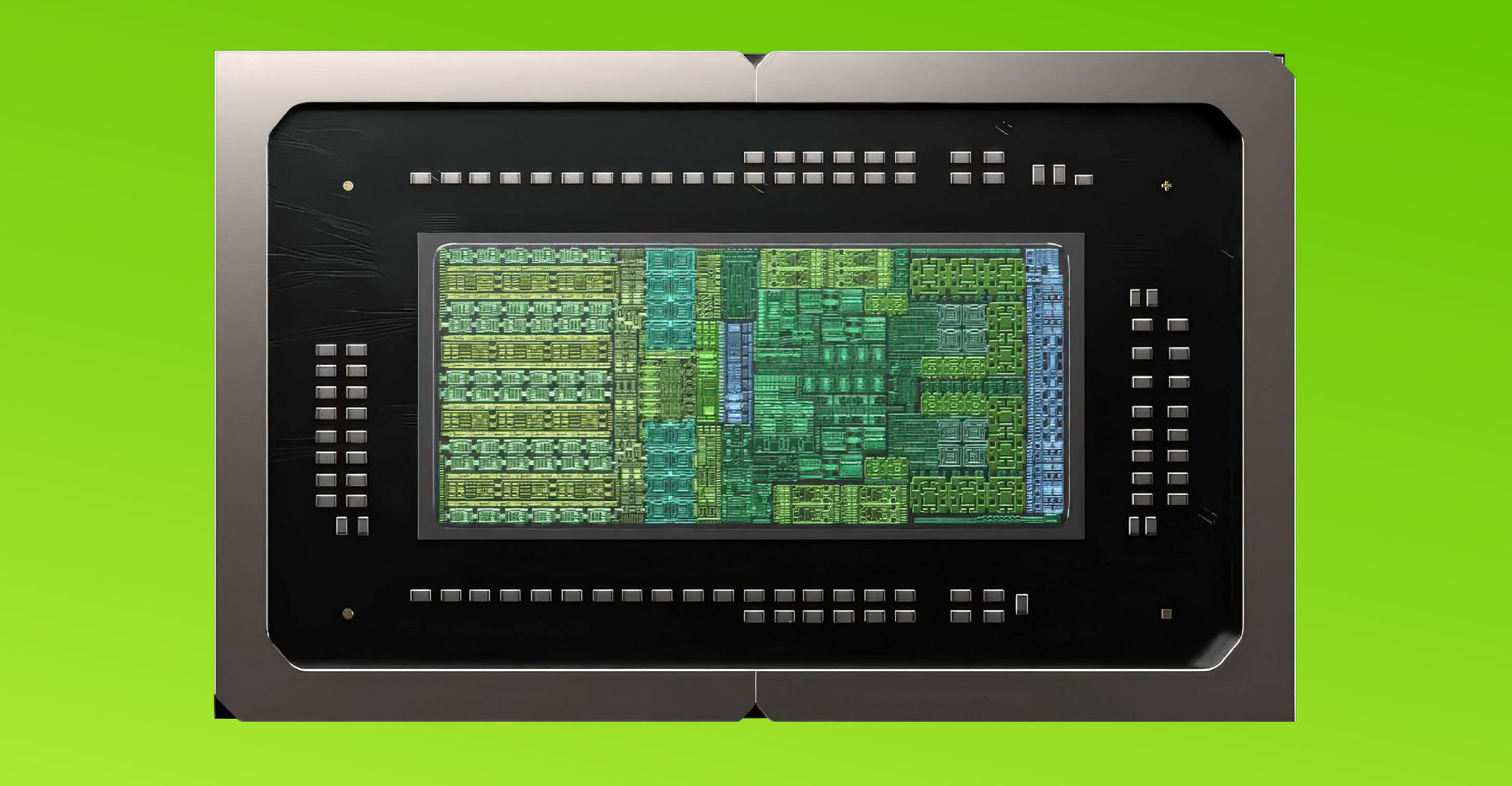

Proč je akcelerátor vybaven serverovým socketem a nese CPUID objasnil leaker Bondrewd, podle něhož je tento produkt vybaven čtveřicí GCD (Graphics Complex Die, grafické čiplety), k nimž jsou připojené CCD (Core Complex Die, procesorové čiplety). Nelze tedy už mluvit o výpočetním GPU, jde o výpočetní APU / SoC.

Protože není jasná doba vydání, nelze z dosavadních údajů spolehlivě odvodit, jaký proces může AMD použít (v podstatě může použít různé procesy pro různé čiplety), jakou architekturu procesorových jader může nasadit (Zen 3, Zen 3 + V-cache, Zen 4, Zen 4 + V-cache - můžeme jen spekulovat na základě toho, že socket SH5 byl dosud spojován s generací Zen 4), ani zda dojde na nějaké pokročilejší HBM2 nebo rovnou na HBM3. Je však dost vysoká šance, že půjde o čip s nejvyšší celkovou plochou křemíku, jaká se kdy v socketu světa x86 procesorů objevila.