Cache, paměťový systém a výkon

Kapitoly článků

Cache a paměťový systém

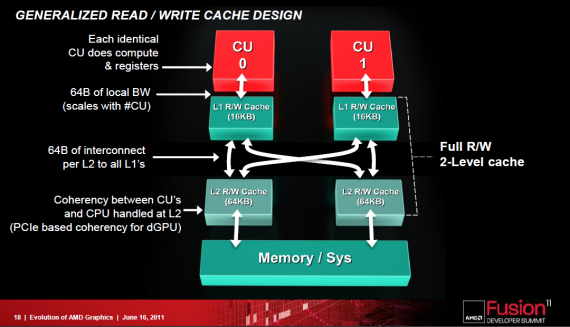

Přepracování se dočkal i dlouho opomíjený systém cache, který byl považovaný za jeden z největších nedostatků současné architektury. Nová L1 cache je unifikovaná (slouží pro data i textury - na rozdíl od Caymanu a Fermi), podporuje komprimované textury (na rozdíl od Caymanu, ale shodně s Fermi).

Každá CU nese 16kB unifikovanou L1 cache (podporuje čtení i zápis), 64kB LDS a 4× 64 kB pro registry (64 kB pro každý SIMD). Pro každé 4 CU je dále sdílena 16kB L1 cache pro skalární výpočetní jednotky a 32kB instrukční L1 cache. Cache druhé úrovně (L2, mimo CU) disponuje kapacitou 64 kB (rovněž podporuje čtení i zápis). Propojení mezi každým blokem CU-L1 i L1-L2 obstarávají 64bit sběrnice.

Budeme-li předpokládat, že čip nese celkem 32 CUs a 256bit paměťovou sběrnici (~ 512 kB L2 cache), nesl by celý čip 11,6 MB paměti, přičemž datová propustnost L1 cache by se pohybovala kolem 1,5 TB/s.

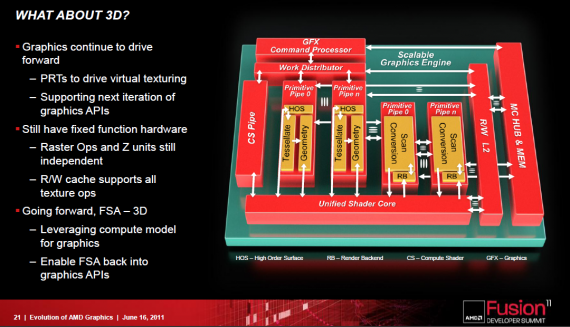

Cache nově podporují i ECC (bez ztráty výkonu), ECC je rovněž implementována i pro VRAM (pravděpodobně ale klasicky, s určitou výkonnostní penalizací). Zajímavou vlastností je práce s virtuálními texturami: Pokud dojde na textury rozměrů, které se nevejdou do paměti (a musely by být velmi pomalu natahovány např. z harddisku), je GCN schopna pracovat pouze s jejich částmi, které jsou v daný okamžik třeba. Jde v podstatě o hardwarovou obdobu Carmackovy technologie Megatexture.

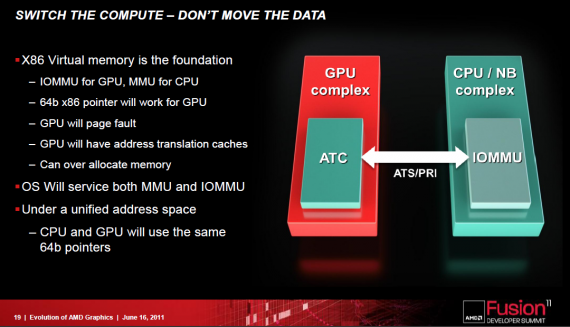

Z výpočetního hlediska zní velice zajímavě podpora x86-64 virtuální paměti (GPU bude obsahovat jednotky pro překlad adresního formátu), jejíž výhody se projeví především v segmentu APU, kde komunikaci mezi GPU a CPU nebrzdí PCI-E.

Výpočetní výkon vs. herní výkon

Pro ATI/AMD byla dlouho těžištěm efektivita při realizaci 3D grafiky. Ze slov Erica Demerse nepřímo vyplývá, že cílem není vylepšení výpočetní stránky bez ohledu na 3D grafiku, ale že se snaží o zlepšení, které nebude degradovat celkovou efektivitu čipu. To je zřejmě poměrně obtížné - již loni u příležitosti vydání čipu Cayman Demers prohlásil, že kdyby bylo na něm a šlo mu pouze o 3D, neopouštěl by VLIW-5. Čip Cayman přinesl architekturu VLIW-4, která byla sice efektivnější pro výpočetní nasazení, ale herní efektivita s vypětím sil zůstala na úrovni staršího čipu Cypress.

Často se objevuje otázka, proč AMD vyvíjela architekturu VLIW-4, pokud na ní chtěla vydat jediný čip: Pro vysvětlení se musíme vydat trochu do minulosti - v době vývoje této architektury v roadmapě TSMC ještě strašil 32 nm proces. AMD pro něj plánovala celou generaci produktů, z nichž jedním měl být čip Cayman (na 32 nm by byl asi tak velký a tudíž i drahý, jako současný Barts / HD 6800). V TSMC nakonec 32nm proces zrušili, AMD přepracovala čip Cayman pro 40 nm proces a čip, který měl být původně vyšším mainstreamem 32nm generace se stal 40nm high-endem. Většina ostatních 32nm VLIW-4 čipů byla zrušena, protože by na 40nm procesu nenabízela o mnoho víc než stávající (VLIW-5) produkty. Cayman ale nebude první a poslední VLIW-4 čip, tuto architekturu budou používat minimálně některá APU Fusion, než ji nahradí GCN.

Ohledně GCN a efektivity v souvislosti s herním výkonem zatím padla jen jedna nejasná zmínka: GCN by měla být jen nepatrně dražší (pokud vůbec) než stávající čipy. Opět ale chybí konkrétní informace (zda dražší ve smyslu výrobních nákladů, ceny produktu, nebo dražší ve smyslu výkonu na milimetr čtvereční či na tranzistor). V každém z možných případů by to ale byla vcelku pozitivní informace, minimálně pro zákazníky. V zájmu AMD je především, aby nová architektura podávala dobré výsledky ve hrách. Pokud by propadla u hráčů a neobsadila dostatečně významnou část trhu, bylo by pro AMD velmi obtížné přesvědčit vývojáře, aby vydávali nové aplikace pro čip s minimálním zastoupením na trhu.

AMD FDS