I Zen 6 Epyc (Venice) se dočkal změny, namísto 4 IOD budou 2

Poslední dobou bylo v kontextu AMD slyšet o několika změnách, které se sice týkají různých sfér a prvků, ale shodně naznačují, že se společnost celkem pragmaticky snaží držet výdaje na uzdě. Na první pohled nemusí být důvody zjevné, finanční výsledky i podíly na trhu v řadě segmentů jsou nejvyšší, jaké kdy společnost měla. Trh IT ale z dlouhodobého hlediska připomíná houpačku a každé období růstu bylo vždy dříve či později následováno propadem.

Připomeňme, že AMD minulý měsíc oznámila propuštění asi 4 % osob, které se má týkat zejména semi-custom divize, které odpadla významná zakázka v podobě SoC pro půlgenerační upgrade Xboxu. V kombinaci s celkovým poklesem poptávky po klasických konzolích to znamenalo snížení příjmů, což vedlo k redukci počtu pracovních sil, pro které není využití. Propouštění má souviset i s nedávnými akvizemi (zejména AI firem), v jejichž důsledku se do společnosti dostaly i osoby na pozicích, které duplikují stávající perzonál (např. účetní, marketing, PR…).

Podobné kroky se však dějí i ve vývoji produktů. Zmínit lze nedávno oznámené zjednodušení vývoje grafických čipů, které se po éře GCN rozdělilo na výpočetní architekturu CDNA a grafickou RDNA, které se v důsledku chybějící koordinace jejich vývoje rozdělilo natolik, že produkty na těchto architekturách postavené vyžadují zcela odlišnou podporu, optimalizace a software. Vice-prezident Jack Huynh v září zmínil, že za současného stavu přinesla změna paměťové hierarchie u jedné architekturu ztrátu použitelnosti stávajících optimalizací pro druhou architekturu, a tak se s každou změnou hardwaru softwarové oddělení vracelo na začátek. Některé zdroje tím vysvětlují i jeden z důvodů zrušení high-endových (čipletových) modelů RDNA 4, které by patrně využívaly onu odlišnou paměťovou hierarchii oproti CDNA.

Nebyla to však jediná změna v grafických plánech. Ještě před ní vyšlo najevo, že AMD zrušila mobilní verzi RDNA 4, která měla podle původní roadmapy debutovat začátkem roku 2025 v APU Kraken. Jenže časem vyplynulo, že další generace APU nedorazí dříve než začátkem roku 2027, kdy již bude k dispozici UDNA (zahájení její výroby se chystá na rok 2026). Jinými slovy, že práce na integrované verzi RDNA 4 by se zúročily pouze na jediném produktu, který ani nemíří do segmentu s vysokými maržemi. Mobilní RDNA 4 tak padla a namísto ní byla využita již hotová RDNA 3.5, navržená od začátku pro nasazení v podobě integrované grafiky.

Roadmapa procesorů Zen (AMD)

Další snahu o efektivnější nakládání s dostupnými prostředky lze vidět ve změnách plánů se Zen 6, který byl původně vyvíjen v podobě osmi-, šestnácti- a třicetidvoujádrových čipletů. Nedávno jsme se dozvěděli, že patrně osmi- a šestnáctijádrové řady nahradila jedna dvanáctijádrová. 32jádrová pro servery zůstala zachována.

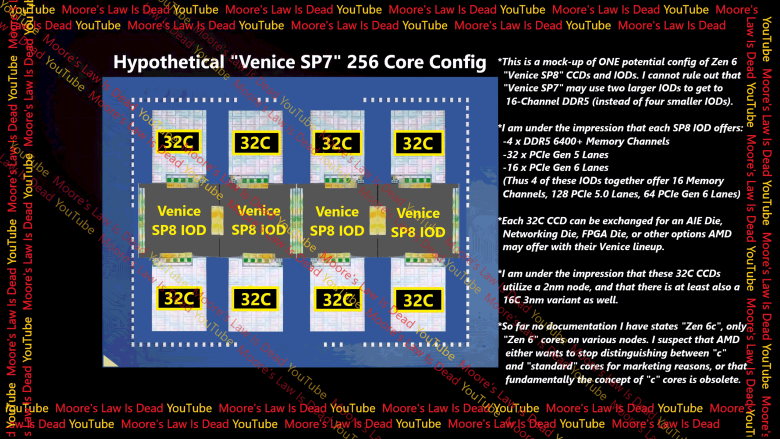

Co se však nejspíš změnilo, je podoba samotného procesoru, který 32jádrové čiplety (CCD) ponese. Podle původních uniklých materiálů měla totiž AMD přistoupit k rozdělení velkého centrálního čipletu na čtyři menší. Ty by tvořily jakýsi řetěz a každý dílek řetězu by připojoval dvojici 32jádrových CCD (případně jiných čipletů potřebných pro daný model procesoru). Podle YouTube kanálu MLID ale AMD situaci přehodnotila a centrální čiplet nebude rozložen na čtyři, ale jen dva.

AMD Epyc Venice / Zen 6, původní podoba (MLID)

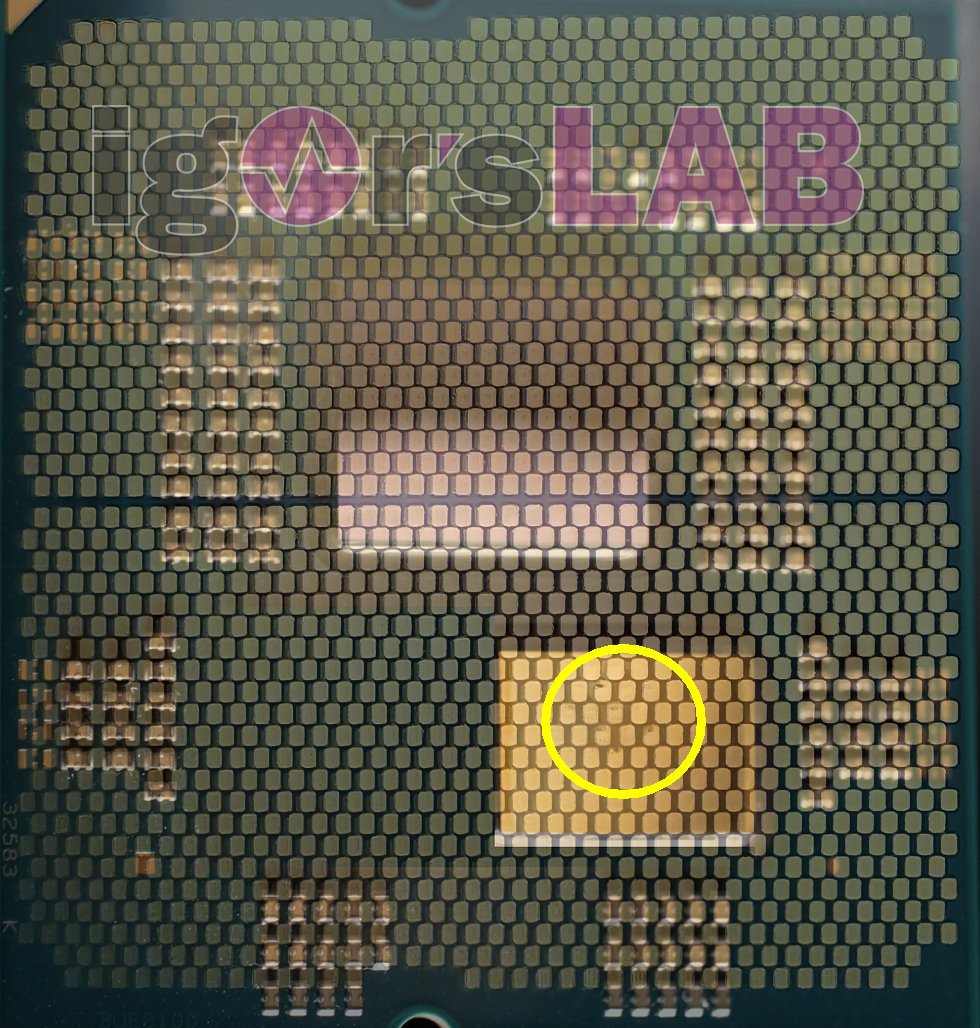

Připomeňme, že rozložení velkého monolitu na čiplety zvyšuje výtěžnost a umožňuje vyšší flexibilitu. I na druhé straně ale existují nějaké meze a zmenšování pod určitou mez přináší zase jiné nevýhody. Je totiž potřeba mít na paměti, že s každým rozložením jednoho kusu křemíku na dva (tři, čtyři…) vzniká nutnost vybavit každý menší kousek křemíku rozhraním pro propojení s těmi sousedními. Což znamená křemík navíc, energetické nároky navíc, potřebu větší křemíkové podložky nebo můstku navíc, softwarové řešení navíc (aby vše fungovalo z hlediska OS a aplikací transparentně) a navíc jde o zdroj potenciálních problémů a tedy potenciální potřebu jejich řešení, které může oddálit vydání produktu.

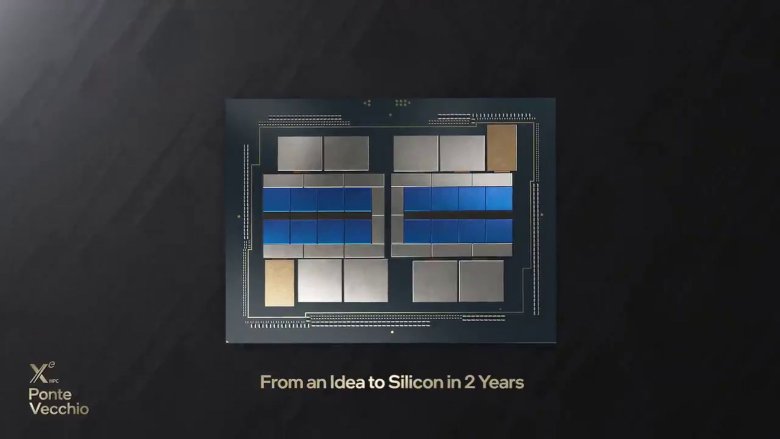

Ponte Vecchio (Intel)

Příkladem může být akcelerátor Ponte Vecchio, od kterého si Intel sliboval urychlení přípravy nového produktu od rýsovacího prkna po hotový křemík na dva roky. Opak byl pravdou a rozložení na hromadu minidlaždiček (63 celkem, z toho 47 funkčních) znamenalo velké zdržení a převálcování ze strany konkurence, která šla cestou, jež se ukázala být podstatně jednodušší.

S Epyc Venice (Zen 6) tedy nejspíš AMD během vývoje zjistila, že čtyři IOD jsou zbytečně vysokým počtem, který nepřináší žádnou natolik zásadní výhodu, aby stály za křemík navíc potřebný pro jejich propojení. IOD patrně budou větší (byť stále podstatně menší než současná) a ke každému budou připojeny až čtyři 32jádrové (nebo jiné) čiplety.

Diskuse ke článku I Zen 6 Epyc (Venice) se dočkal změny, namísto 4 IOD budou 2