Intel hovoří o budoucnosti a 80jádrovém procesoru

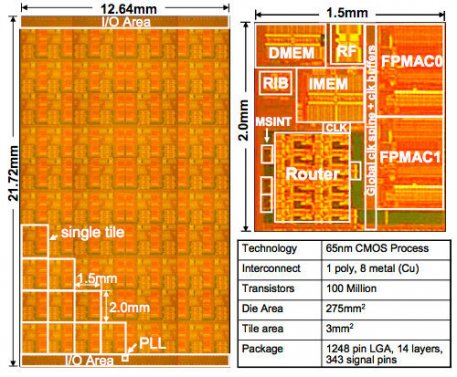

Čip, o kterém hovoříme, má plochu jádra jen o trochu větší než Core 2 Duo (oba jsou vyráběny 65nm technologií). Zatímco Core 2 Duo se rozkládá na 143 mm², „TeraFLOPS čip“ má rozlohu 275 mm². I tak má menší počet tranzistorů, jen asi 100 miliónů oproti 291 miliónům u Core 2 Duo. Důvodem tohoto relativního nepoměru je fakt, že Core 2 Duo obsahuje z hodně velké části hlavně L2 cache, zatímco „TeraFLOPS čip“ jsou většinou spoje mezi tranzistory, které zatím nejde tak dobře zkrátit.

Každé z 80 jader tohoto čipu, která jsou poskládána v matici 8 × 10, je velké 3 mm² (2 × 1,5). Vedle toho celý procesor ještě obsahuje I/O části pro komunikaci se zbytkem systému. Procesor, který takový kousek křemíku nese, má (stejně jako třeba desktopové Core 2 Duo) jen plošky, pasuje tedy do LGA patice se 1 248 piny. Zajímavé je, že jen 343 z těchto pinů jsou signálové, zbytek je převážně napájení a uzemnění.

Každé z 80 jader tohoto čipu, která jsou poskládána v matici 8 × 10, je velké 3 mm² (2 × 1,5). Vedle toho celý procesor ještě obsahuje I/O části pro komunikaci se zbytkem systému. Procesor, který takový kousek křemíku nese, má (stejně jako třeba desktopové Core 2 Duo) jen plošky, pasuje tedy do LGA patice se 1 248 piny. Zajímavé je, že jen 343 z těchto pinů jsou signálové, zbytek je převážně napájení a uzemnění.

Pracovní frekvence tohoto procesoru je 3,16 GHz a v takovém případě dělá při spotřebě pouhých 62 W právě 1 (přesněji 1,01) TeraFLOPS. Takového výkonu dosáhl poprvé v roce 1996 superpočítač ASCI Red poskládaný na ploše 186 m² a čítající skoro 10 000 procesorů Pentium Pro na 200 MHz. Jeho spotřeba byla půl megawattu.

„TeraFLOPS čip“ lze samozřejmě přetaktovat, s tím však rapidně klesá jeho efektivita výkonu na watt. Při přetaktování na 5,1 GHz dosahuje výkonu 1,63 TeraFLOPS, ovšem spotřeba je už 175 W. Na 5,7 GHz dokáže udělat 1,81 TeraFLOPS za cenu 265 W. Proto půjdou vědci raději cestou paralelizace než zvyšování frekvence.

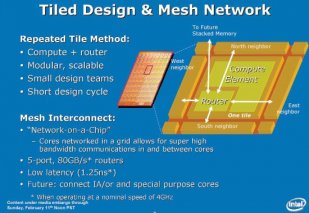

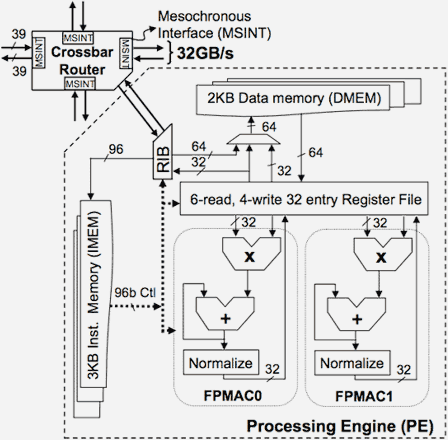

Pokud jde o jedno samotné jádro tohoto čipu, hovoříme o velice jednoduchém „Processing Engine“ (PE) obsahujícím dvě FPMAC jednotky, 3 kB instrukční a 2 kB datové paměti (cache), 10portový registr a hlavně 5portový „Crossbar Router“ sloužící ke komunikaci s ostatními jádry (přesněji k předávání dat mezi jádry). Čtyři komunikují se sousedními jádry, přičemž jedno takovéto rozhraní MSINT má datovou propustnost 32 GB/s. Pátý port bude využit později pro komunikaci s pamětí v další vrstvě křemíku, k čemuž prý dojde možná už v dalším čtvrtletí. Právě onen „Crossbar Router“ je základním kamenem každého malého jadérka procesoru. Samotné jádro totiž může být klidně nejen jednoduchý PE, ale třeba x86-kompatibilní jádro, případně specializovaná část pro šifrování dat a podobně. Nakonec ani těch jader nemusí být 80, představte si třeba 16jádrový x86-kompatibilní procesor s dalšími výpočetními jednotkami specializovanými na šifrování dat, výpomoc pro protokol TCP/IP nebo počítání RAID polí, 3D renderování a tak dále.

Tento konkrétní procesor je však velice jednoduchý, je postaven na 96-bit VLIW architektuře. Do jedné takové „VLIW instrukce“ lze zakódovat najednou nejvýše 8 operací (takovou operací může být FPMAC, load/store nebo třeba instrukce pro Crossbar Router libovolného jádra, protože tyto routery si samy předávají instrukce dál). Jedna floating-point operace (s plovoucí řádovou čárkou) se však v tomto případě nedá rovnat s tradiční 128bitovou FLOP dnešních procesorů, FPMAC jednotky jsou 32bitové „fully pipelined“ a každá provádí jednoduchou FP operaci. Samotná jednoduchost čipu a stavby jádra tak limituje možné použití v reálném prostředí, nicméně Intel stejně nehodlá takovýto procesor prodávat. Výzkumný projekt „Tera-scale“ je základní nástroj hledání nových možností obecných a specializovaných procesorů, funkčnosti jader a způsobů propojení čipů mezi sebou a s počítačem, které umožní co nejlepší přenosy dat a především návrh softwaru, který dokáže možnosti vícejádrových procesorů maximálně využít.

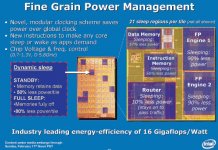

Pokud jde o řízení spotřeby, každé jádro má 21 částí, které mohou být nezávisle vypínány a šetřit tak energii. Vzato kolem a kolem, FP jednotky při nečinnosti ušetří až 90 % energie pro ně jinak potřebné, datová i instrukční paměť skoro polovinu při pouhém udržování dat (a 80 % při úplné nečinnosti). Nejzaměstnanější částí je onen router, který předává data sousedním jádrům.

Procesor také umí efektivně rozkládat zátěž. Tím je zajištěno, aby nevznikaly oblasti, kde by více jader blízko u sebe pracovalo, zatímco ostatní jádra by nic nedělala. V takovém případě se zátěž přenese na některá jádra vzdálenější a tím se produkované teplo rozloží do větší plochy.

Problémovou částí se však v případě vícejádrových procesorů stává nedostatečně svižná komunikace se zbytkem systému, především s operační pamětí. Dnešní dvou– a čtyřjádrové procesory Intelu používají tzv. „Front Side Bus“, sběrnici, jejíž zvyšující se rychlost již začíná být na hranici únosnosti a s přibývajícím počtem jader to bude procesor hodně brzdit. Nakonec ale i samotné paměti se dostávají do stavu, kdy je budeme moci nazývat brzdou systému. Zvyšující se počet paměťových kanálů pak také není tím pravým ořechovým. Třeba takový 6kanálový řadič by vyžadoval zhruba 1 800 pinů – zkuste to nějak rozumně pak natahat na základní desku!

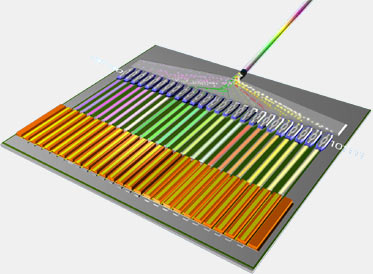

Jistým řešením je vytvoření další úrovně cache – a protože se dnes již svět ubírá k L3 cache, byla by tato už vlastně L4 cache. Problém je, že cache na úrovni jádra procesoru zabírá hodně místa a křemíková plocha, na níž se tvoří procesory, není zrovna levný materiál. V Intelu na to však jdou od lesa a vyvíjejí tzv. „3D Stacking“ nebo také „Die Stacking“ – jakési „štosování“ (korektněji spíše asi „stohování“) jednotlivých vrstev na sebe (podobnost se Samsungovou technologií WSP nejspíše nebude náhodná ;-). Na procesoru by tak mohla přímo ležet vrstva nějaké té DRAM, která by komunikovala s procesorem nesrovnatelně svižněji než operační paměť v PC (nehledě na velmi malé latence v případě takto blízkého umístění). Jistou výhodou pak může být i výtěžnost při výrobě takových procesorů – čím méně součástí na jedné vrstvě, tím menší množství materiálu se pak při nezdaru vyhodí. Padla také zmínka o kapacitě této „L4 cache“: jedna vrstva by mohla pojmout nějakých 256 MB, přičemž vrstev může být případně i více.

Ačkoli hovoříme o velikosti cache srovnatelnou s RAM v dnešních low-endových počítačích, nutnosti mít „skutečnou operační paměť“ se tímto nezbavíme a tudíž je třeba i tak uvažovat o nějaké svižné komunikaci se zbytkem systému. Jako jisté řešení se jeví hybridní laserový křemík, který dokáže optickou cestou přenášet data výrazně rychleji než tradičním „drátováním“. V době, kdy firma Intel svůj hybridní laserový křemík představila, hovořila o spoji sdružujícím 25 paprsků o různých vlnových délkách při přenosové kapacitě kolem jednoho terabitu za sekundu.

Nakonec jen dodejme představy Intelu o reálném nasazení právě vyvíjených technologií. Asi tak za 5 až 10 let můžeme očekávat nasazení něčeho z toho, o čem jste si dnes mohli přečíst (ať už to budou vícejádrové procesory s routerem u každého jádra či vrstvení křemíků na sebe). Důležité je, že vše bude rychlejší a nemělo by to chtít o moc větší příděl energie než dnes.