S Alterou to nevyšlo, do Xeonů bude Intel integrovat logiku eASIC

Podle agentury Reuters a zpravodajského portálu The Wall Street Journal plánoval Intel v březnu letošního roku akvizici společnosti Altera v hodnotě $10 miliard. V průběhu dubna se začaly objevovat zvěsti, že Altera nabídku z neupřesněného důvodu odmítla a vyjednávání tím skončila.

Nynější oznámení o spolupráci se společností eASIC, která nabízí obdobné produkty, můžeme chápat jako potvrzení neúspěšné akvizice. eASIC vyvíjí mimo jiné logické obvody, které (podle slov této společnosti) nabízejí programovatelný potenciál FPGA v kombinaci s výkonem a flexibilitou ASIC při energetických nárocích dosahujících jen zlomku spotřeby FPGA.

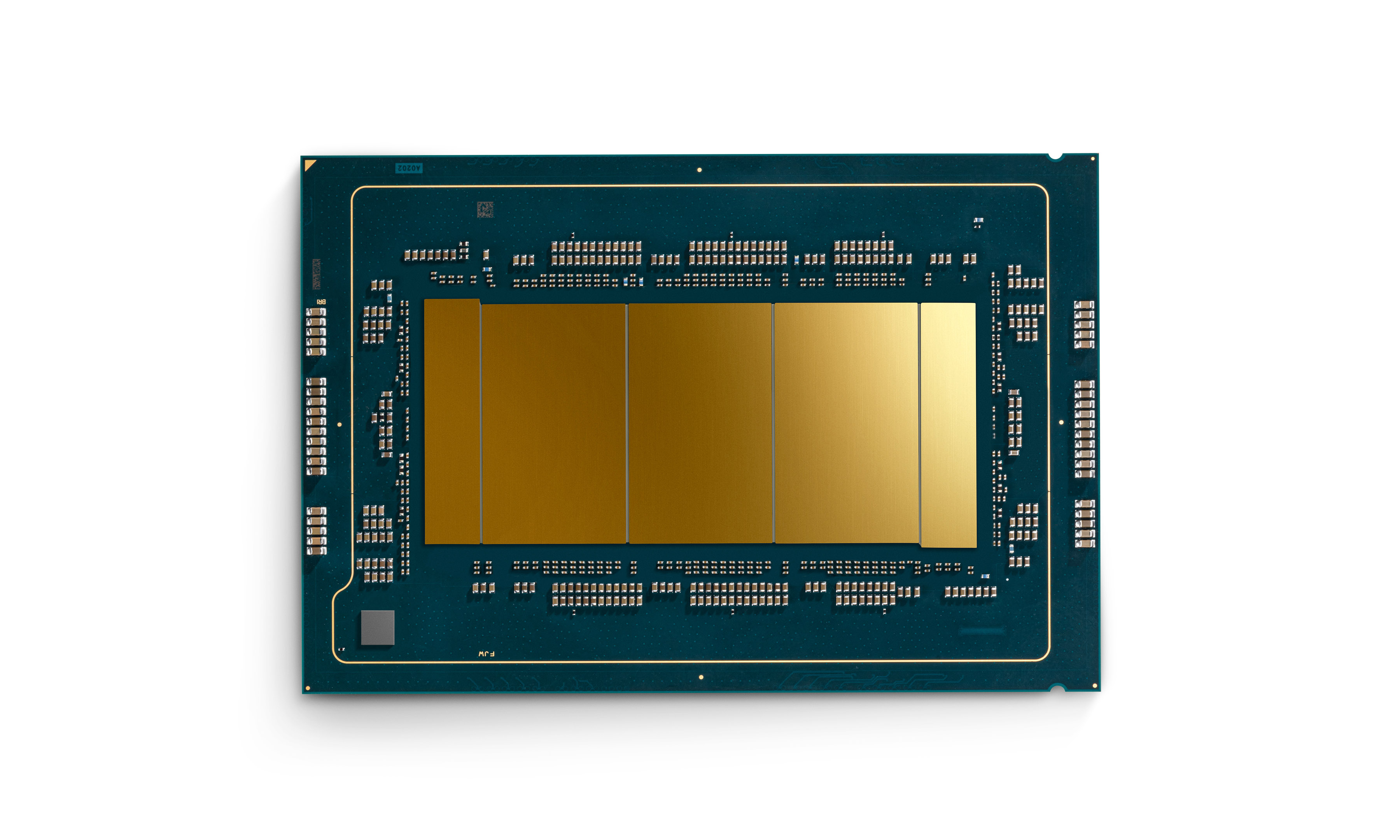

Intel oznámil, že budoucí generace Xeonů rozšíří právě o tuto logiku. Bližší informace ale neupřesnil. Jsou v podstatě dvě základní možnosti: buďto logiku od eASIC (jako samostatný kousek křemíku) integrovat do společného pouzdra vedle jádra Xeonu, nebo - za předpokladu užší spolupráce - integrovat logický obvod přímo do křemíkového jádra Xeonu jakožto monolit.

Lze připustit i cestu evolučního vývoje: nejprve dojde na volnější propojení a po rozvinutí spolupráce se přistoupí ke spojení obou jader dohromady - případně Intel koncept přizpůsobí cílovému segmentu a cenové politice. Jisté je jedno: Intel má velké množství peněz, které půjdou na rozvoj produktů s programovatelnými obvody. Tyto peníze mohla mít Altera, ale ta se jich vzdala ve prospěch jednoho ze svých konkurentů, jehož úlohu v blízké době spolupráce s Intelem posílí.