Lisa Su demonstrovala 3D cache na Ryzenu o 15 % navyšující herní výkon

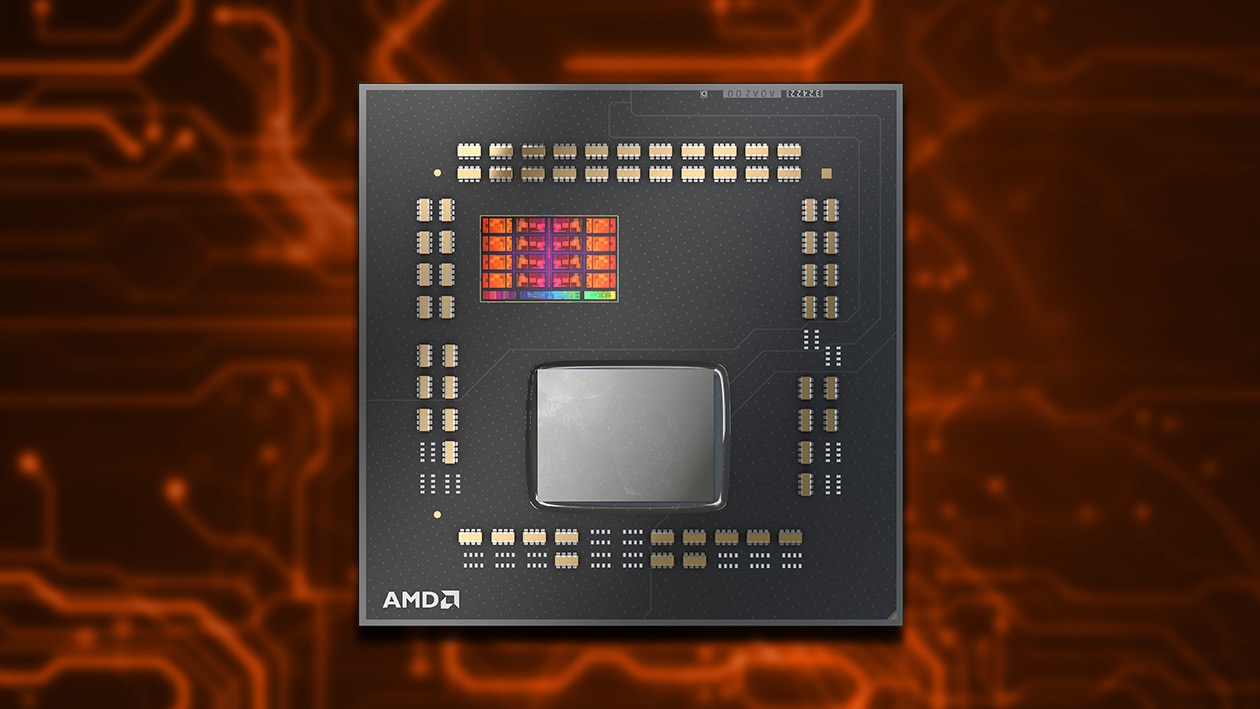

CEO AMD Lisa Su na Computexu ukázala vzorek dvanáctijádrového procesoru s jádry Zen 3, který nese na každém procesorovém čipletu navrstvenou 64MB L3 cache. Ta dosahuje plochy 6×6, tedy 36 milimetrů čtverečních.

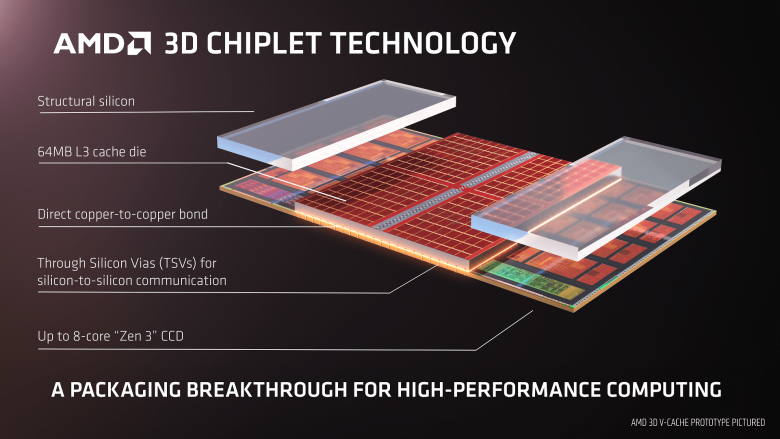

Okolí cache je vyplněno neaktivním křemíkem pouze pro zarovnání čipletu. Pro samotný čiplet i navrstvenou L3 cache je použit ztenčený křemík, aby mohla být zachována současná technologie pouzdření a nebylo potřeba vyšších pouzder.

Pro spojení čipletu s vrstvou L3 cache je použita technologie Chip on Wafer / Silicon on Silicon, která oproti propojení čipletů přes pouzdro dosahuje >200× vyšší denzity spojů (tedy širší sběrnice), >15× vyšší denzity spojů oproti technologii Micro Bump využívané např. Intelen v projektu Foveros / Lakefield a >3× vyšší energetické efektivity propojení oproti Micro Bump. Díky takto široké sběrnici dosahuje přidaná L3 cache datové propustnosti přes 2 TB/s, čímž překonává i propustnost L1 cache, ovšem zůstávají latence obvyklé pro L3 cache.

Su prezentovala výkonnostní výsledky ve hrách testovaných v rozlišení 1080p na Ryzenu 9 5900X a obdobě tohoto procesoru s navrstvenou +2× 64 MB L3 cache (192 MB celkem); u obou procesorů s nastavenou stabilní taktovací frekvencí 4 GHz. Průměrný herní výkon se zvýšil o 15 %, což odpovídá generačnímu skoku.

Lisa Su potvrdila, že technologie bude využita ve výrobě ještě letos pro nespecifikované high-end produkty. Může jít o serverové procesory Epyc, může jít o high-endové modely procesorů Ryzen. V tomto kontextu už se jeví jako vcelku pochopitelné, že si AMD mohla dovolit zrušit 6nm půlgeneraci Zen 3+ / Warhol. Existovaly totiž dvě alternativy, mezi kterými vybírala a volba nejspíš padla na 3D čiplety.

Vrátíme-li se u Epyců, v jejichž kontextu jsme vás o nasazení vrstvených čipletů informovali minulý týden, dopadla situace v podstatě podle nejpravděpodobnějšího scénáře:

| Nejjednodušší by patrně bylo navrstvit SRAM na existující nebo k tomu upravené čiplety, čímž by se řešení vyhnulo nákupu HBM od externího dodavatele, podložkám a složitějšímu pouzdření. To už je samozřejmě jen spekulace. Patrně ale nebude trvat dlouho a dozvíme se další podrobnosti. |

Epycu se totiž týkala informace, že řada s 3D čiplety ponese až ~1GB cache. To se v kontextu výše uvedených informací jeví jako snadno realizovatelný krok: Ryzen, který Lisa Su ukazovala, nesl na čipletu navrstvených 64 MB L3 cache, která zabírala 36 mm², což není ani polovina plochy čipletu. AMD tudíž v serverovém segmentu může nasadit 128MB L3 cache, se kterými se při osmi čipletech na procesor dostáváme k celkem 1024 MB přidané L3 cache. Tedy k onomu 1 GB.

Pokud by AMD chtěla tento 1 GB realizovat přes HBM, musela by k připojení 1GB HBM2 čipu připravit speciální čiplet s rozhraním pro HBM, tento připojit k HBM prostřednictvím křemíkové podložky (interposer) a výsledkem by byla 1GB cache o datové propustnosti ~300 GB/s. Při alternativě, kterou AMD použila, tedy navrstvením SRAM, má 1GB cache i bez potřeby interposeru, bez marží výrobce pamětí a s datovou propustností 4× ~2 TB/s, tedy 8 TB/s, což je asi 26× rychlejší řešení než použití 2,4GHz HBM2.