Proces N3P bude pro zákazníky TSMC nejzajímavější, výroba začne ve 2. pololetí

Těmi důvody bychom rovnou mohli začít. Vyplývají totiž z možností vývoje i parametrů:

- N3 - původně plánovaná základní verze 3nm procesu TSMC, nevyšla podle plánu a byla nahrazena N3B (pokud dnes někdo referuje o N3, zpravidla myslí N3B)

- N3B - skutečně první dostupná verze 3nm procesu TSMC, aktuálně ji využívá především Apple

- N3E - od loňského roku dostupná verze, která však není kompatibilní s N3B (z N3B nelze přejít na N3E bez úpravy návrhu), nabízí o něco vyšší energetickou efektivitu a takty, oproti původní N3 také FinFLEX (možnost použít pro různé části čipu odlišnou subvariantu procesu optimalizovanou na výkon nebo plochu a spotřebu)

- N3P - kompatibilní nástupce („die-shrink“) N3E, který nabízí o 5-10 % nižší spotřebu nebo o ~5 % vyšší výkonu plus o několik procent vyšší denzitu

- N3X - proces optimalizovaný na výkon chystaný na rok 2025

Z tohoto přehledu je zřejmé, že výrobci, kteří nepotřebovali 3nm proces nasadit skutečně nutně, neměli důvod volit N3B, protože by na něm uvízli - nemohli by s návrhem čipu přejít na lepší variantu procesu bez úprav návrhu. Z toho hlediska se pro řadu výrobců stala preferovanější varianta N3E. S ohledem na různá zpoždění na různých stranách nakonec většina 3nm zákazníků TSMC, která původně uvažovala o N3E, využije N3P, protože již bude dostupný a jejich návrh (původně určený pro N3E) je s N3P kompatibilní.

Lze tedy očekávat, že chystané 3nm návrhy AMD a Nvidie budou z větší části využívat právě N3P. Jiná bude situace u Intelu. Ten pro PC segment chystá procesory Arrow Lake (původně Intel 20A) a Lunar Lake (původně Intel 18A). Z důvodu problémů na straně nových procesů Intelu nakonec Intel využije 3nm kapacit TSMC. Pro Arrow Lake většinově (pouze desktopové čipy s nižším počtem jader vzniknout na Intel 20A), pro Lunar Lake čistě. Z uniklých materiálů Intelu vyplývá, že Arrow Lake cílí na proces N3B a Lunar Lake na N3P, nicméně tyto materiály již nemusejí být zcela aktuální a některé zdroje uvádějí, že i Lunar Lake by mohla zůstat na starším N3B. Důvodem by mohla být právě skutečnost, že sériová výroba na N3P začíná ve druhém pololetí, výroba čipu zabere alespoň pět měsíců a Intel chce právě ve druhém pololetí Lunar Lake vydat. S N3P (pokud by tedy várka procesorů připravená k vydání nevznikla ještě před fází sériové výroby podobně jako třeba Cannon Lake) by to mohl být problém.

SRAM / cache, nepřítel 3nm výroby

Již delší dobu je známo, že paměť typu SRAM, která se používá především jako cache, s novými procesy přestává škálovat. SRAM na 3nm procesech TSMC zabírá totožnou plochu jako na 5nm procesu stejného výrobce (u některých variant o pár procent méně, ale to není hmatatelný přínos). Jinými slovy cache zůstává i při přechodu na novější proces stejně velká (plochou spotřebovaného křemíku). Protože je každý nový proces dražší, znamená to, že obvody, které nezmenší, budou paradoxně dražší než na starším procesu.

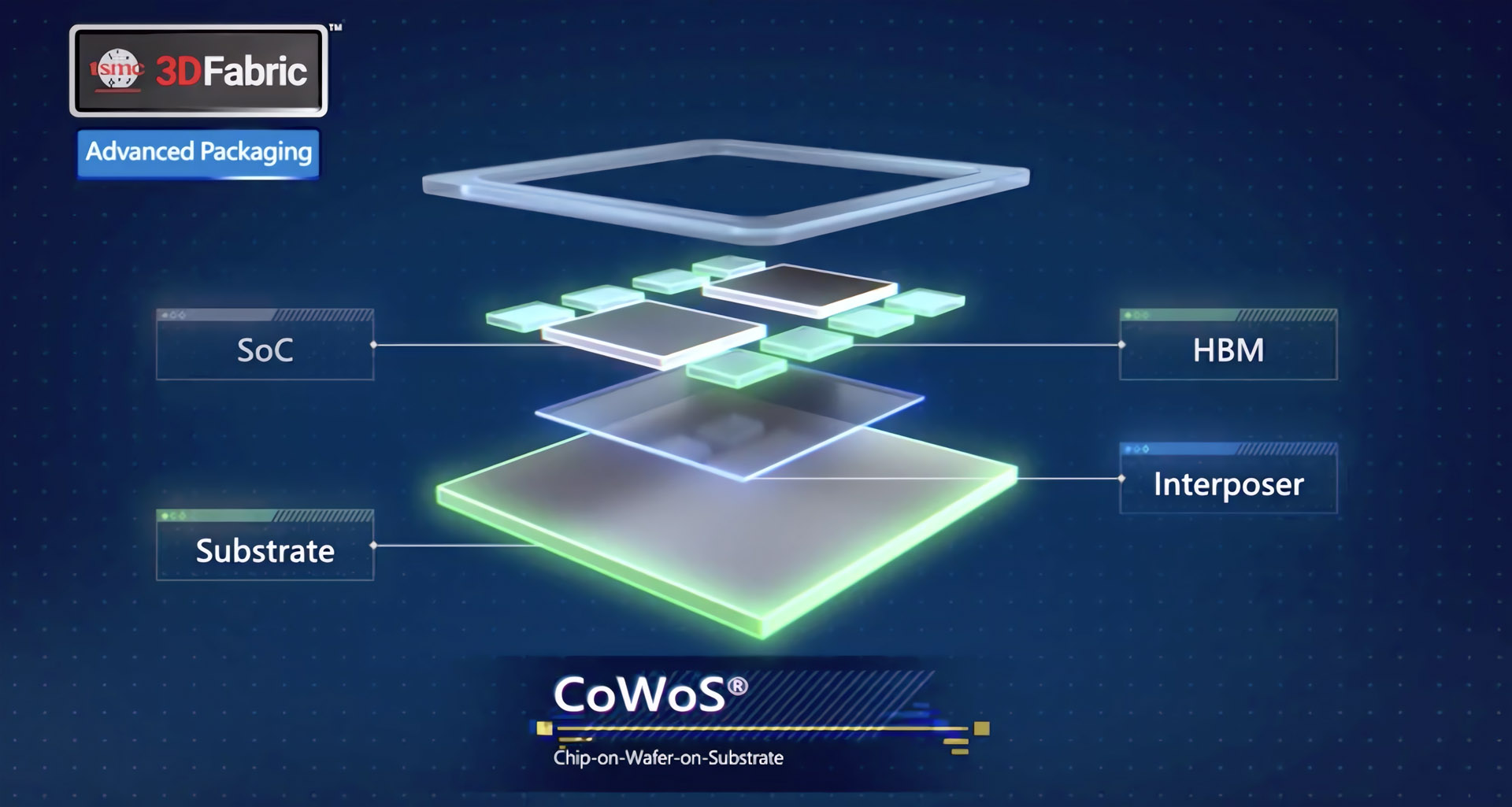

Pro výrobce hardwaru je tedy stále větší motivací oddělovat prvky bohaté na SRAM do samostatných čipletů / dlaždic / vrstev / podložek, zkrátka do samostatných kousků křemíku a ty vyrábět cenově optimálním procesem (dnes především 6nm, časem možná 5nm až 4nm). Lze proto předpokládat, že koncepty, se kterými přišla AMD (např. V-cache na procesorech X3D, podložky integrující cache na Instinct MI300 nebo čiplety s cache a řadičem jako na Radeonech RX 7000) budou čím dál běžnější. Nároky na cache (s ohledem na pomalejší vývoj v segmentu pamětí) rostou a integrovat vyšší desítky až stovky MB cache do 3nm procesu a novějších je v segmentu, kde se hledí na poměr cena / výkon, ekonomická sebevražda.