Strix Halo je testovací platforma pro Zen 6, využívá InFO pouzdření

Když se objevily zprávy o tom, že se čiplety Zen 5 určené pro APU Strix Halo budou nějakým způsobem lišit od Zen 5 čipletů určených pro desktopové a serverové procesory, dovolil jsem si vyslovit domněnku, že rozdíl bude spočívat v odlišném rozhraní. Tedy v rozhraní určeném k propojení pomocí podložky namísto stávajícího rozhraní určeného k propojení čipletů přes substrát pouzdra.

Propojení pomocí podložky je dražší, ale umožňuje dosažení vyšší přenosové rychlost, nižší latencí a/nebo nižších energetických nároků. Rychlejší a efektivnější spojení mezi procesorovými čiplety a integrovanou grafikou se právě u mobilního zařízení hodí.

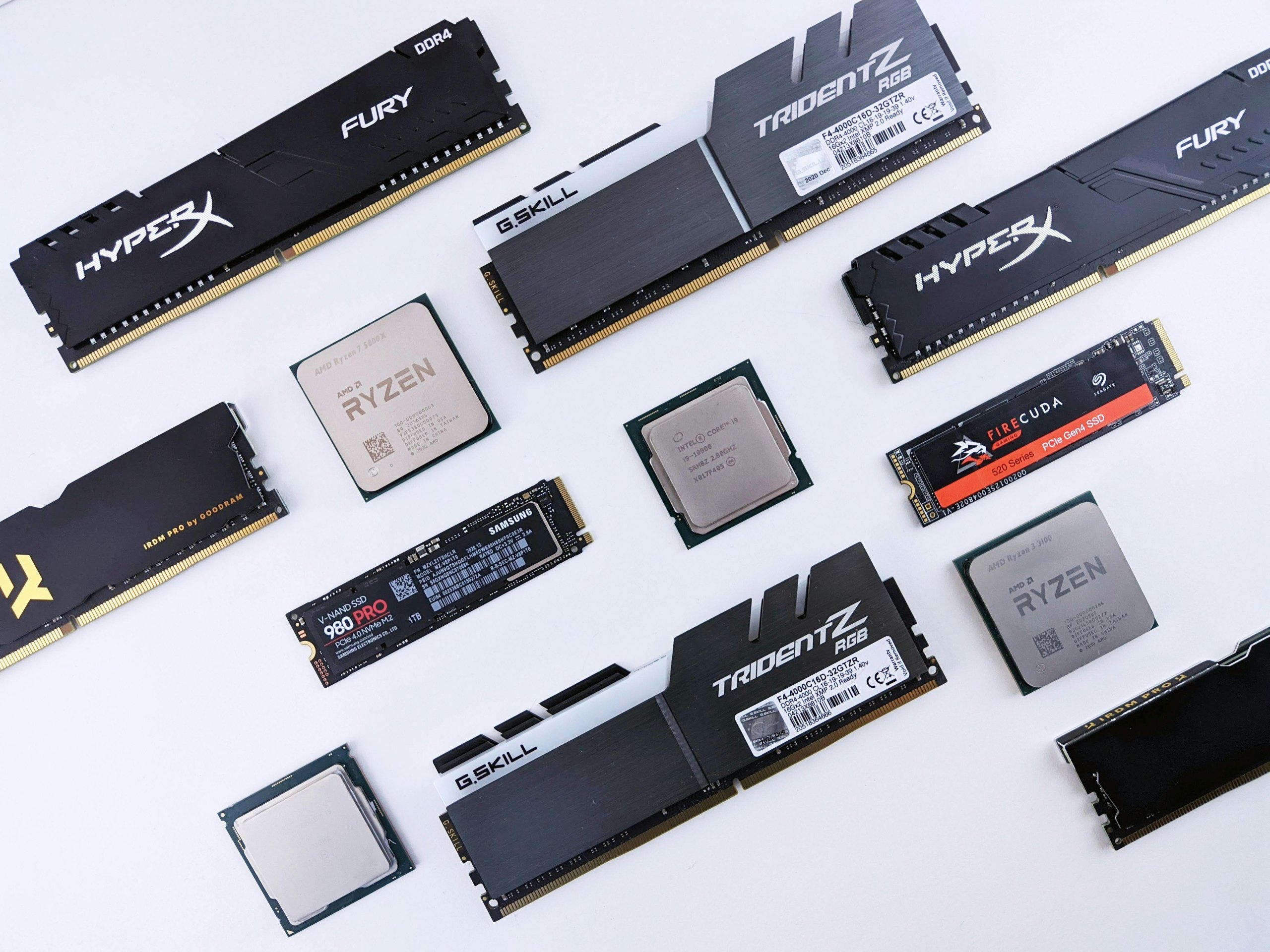

Pouzdřící technologii InFO nabízí TSMC v široké škále variant optimalizovaných pro různé účely (TSMC)

Leaker Olrak_29 právě tuto možnost potvrdil a upřesnil i dvě další skutečnosti. Tou první je způsob propojení, použita bude technologie TSMC InFO alias Integrated Fan Out alias Chip First (oproti CoWoS alias Chip Last). Technologie InFO existuje v celé řadě variant specializovaných pro různé účely (pro Strix Halo by se mohla hodit například InFO_LSI nebo InFO SOIC). Důvodem pro volbu InFO však bude v zásadě skutečnost, že je z hlediska potřeb tohoto řešení vhodnou alternativou k pouzdření typu CoWoS, jehož kapacity jsou dlouhodobě rozebrané pro pouzdření výkonných AI akcelerátorů.

InFO_LSI lze použít k velmi podobným účelům jako CoWoS (TSMC)

Druhým zásadním zjištěním pak je, že Strix Halo v tomto ohledu budou sloužit jako určitý předvoj či testovací platforma pro Zen 6, se kterým má právě na novější typ pouzdření přejít podstatná část portfolia, přinejmenším serverového.

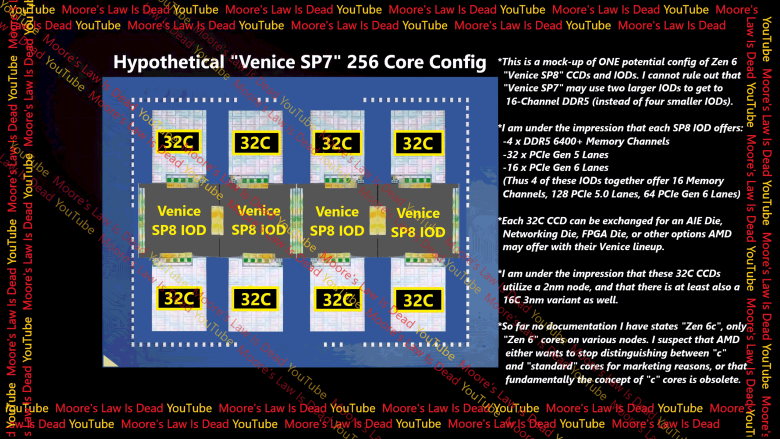

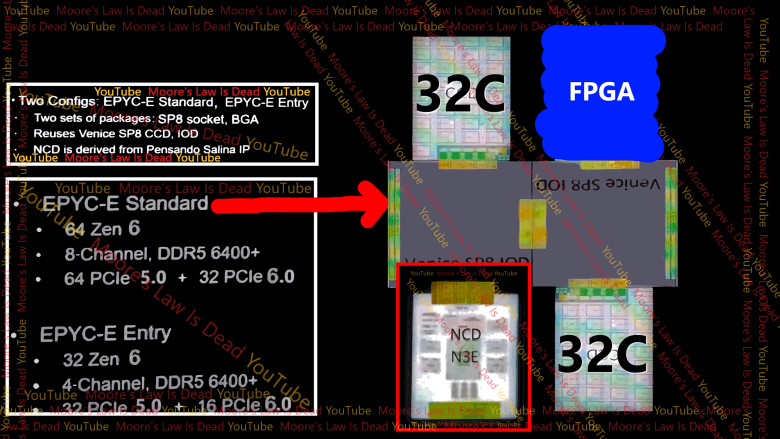

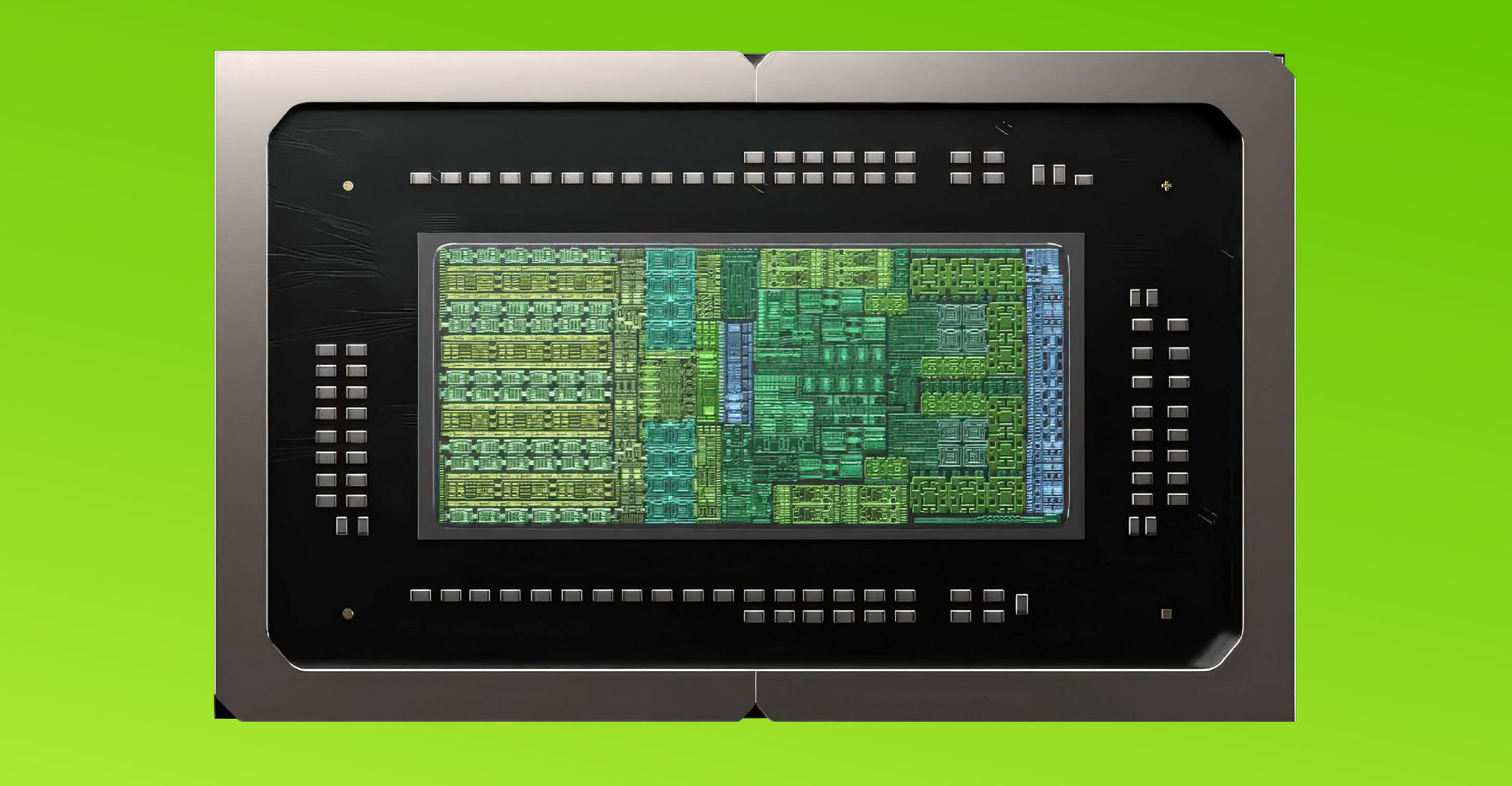

Nové čiplety s Epycy Zen 6 podle MLID

Právě zavedení nového konceptu čipletů u procesorů Epyc na bázi Zen 6 koncem loňského roku avizoval YouTube kanál MLID. Naznačil škálující (zřetězitelné) IOD (centrální čiplety), na které by díky unifikovanému rozhraní bylo možné flexibilně připojovat procesorové čiplety nebo různé akcelerátory, podle potřeby.

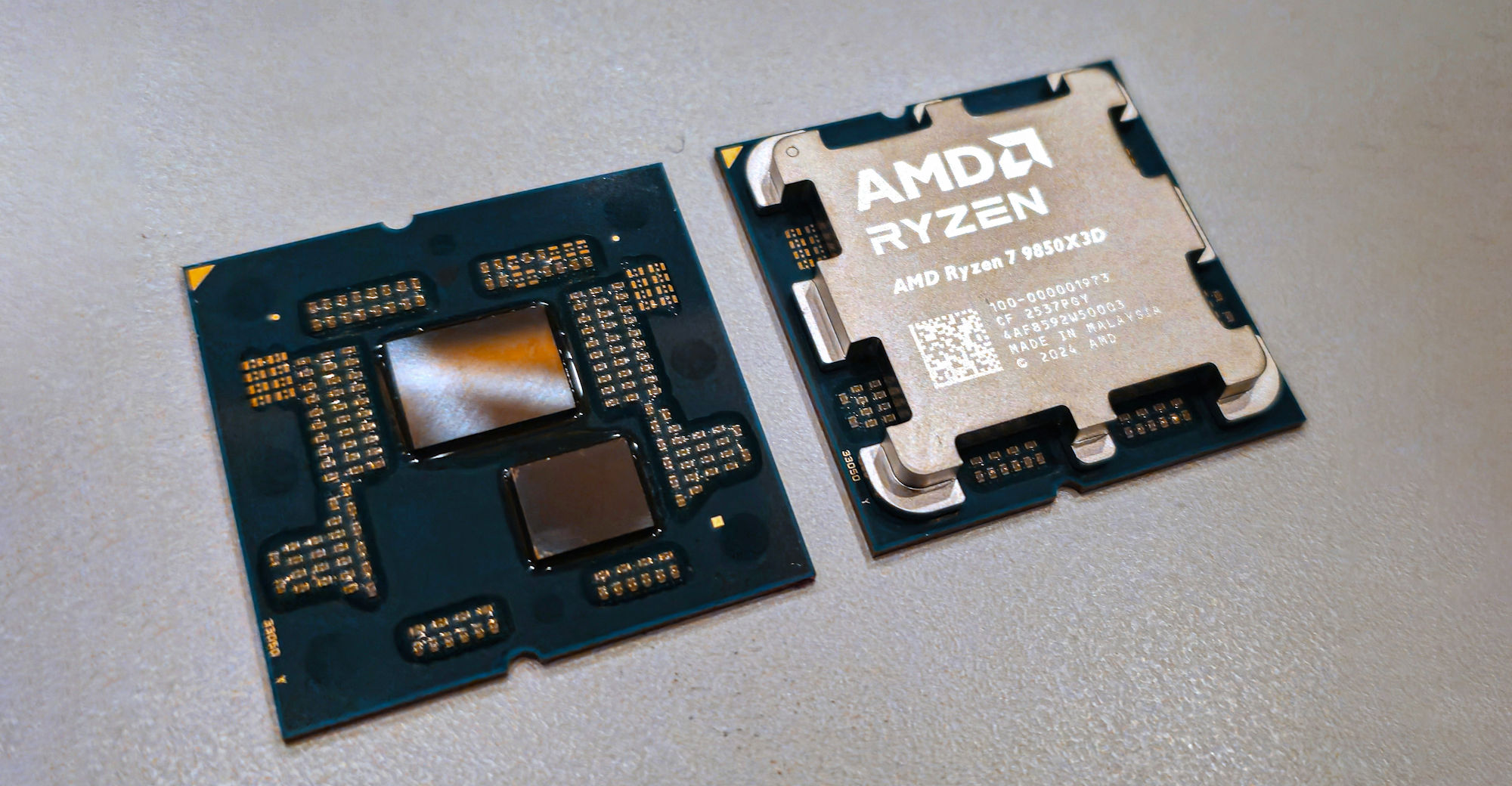

APU Strix Halo je první čipletové APU od AMD. Skládat se bude ze dvou čipletů s osmi jádry Zen 5 (celkem tedy 16 jader) a centrálního čipletu, který obsahuje velkou integrovanou grafiku (2560 stream-procesorů RDNA 3.5, tzn. 2,5× Strix Point, 3,3× Phoenix), AI akcelerátor XDNA2 o výkonu (podle některých zdrojů) ~60 TOPS, úspornou variantu jádra či jader Zen 5, 256bit sběrnici pro paměti LPDDR5X-8533 a 32 MB cache poslední úrovně (MALL / SLC), která by podle dostupných zdrojů měla sloužit grafice i procesorovým jádrům (z principu všem obvodům přistupujícím k operační paměti, tedy i AI akcelerátoru ap.).