Unikly specifikace platformy / procesorů AMD Vermeer (Zen 3 pro AM4)

Tři strany ze specifikací platformy Vermeer v podstatě potvrzují očekávané a vyvracejí některé divoké spekulace (kterým jsme se ale na DIIT nevěnovali, takže - pokud jste je nečetli jinde - vás níže uvedené materiály nepřekvapí).

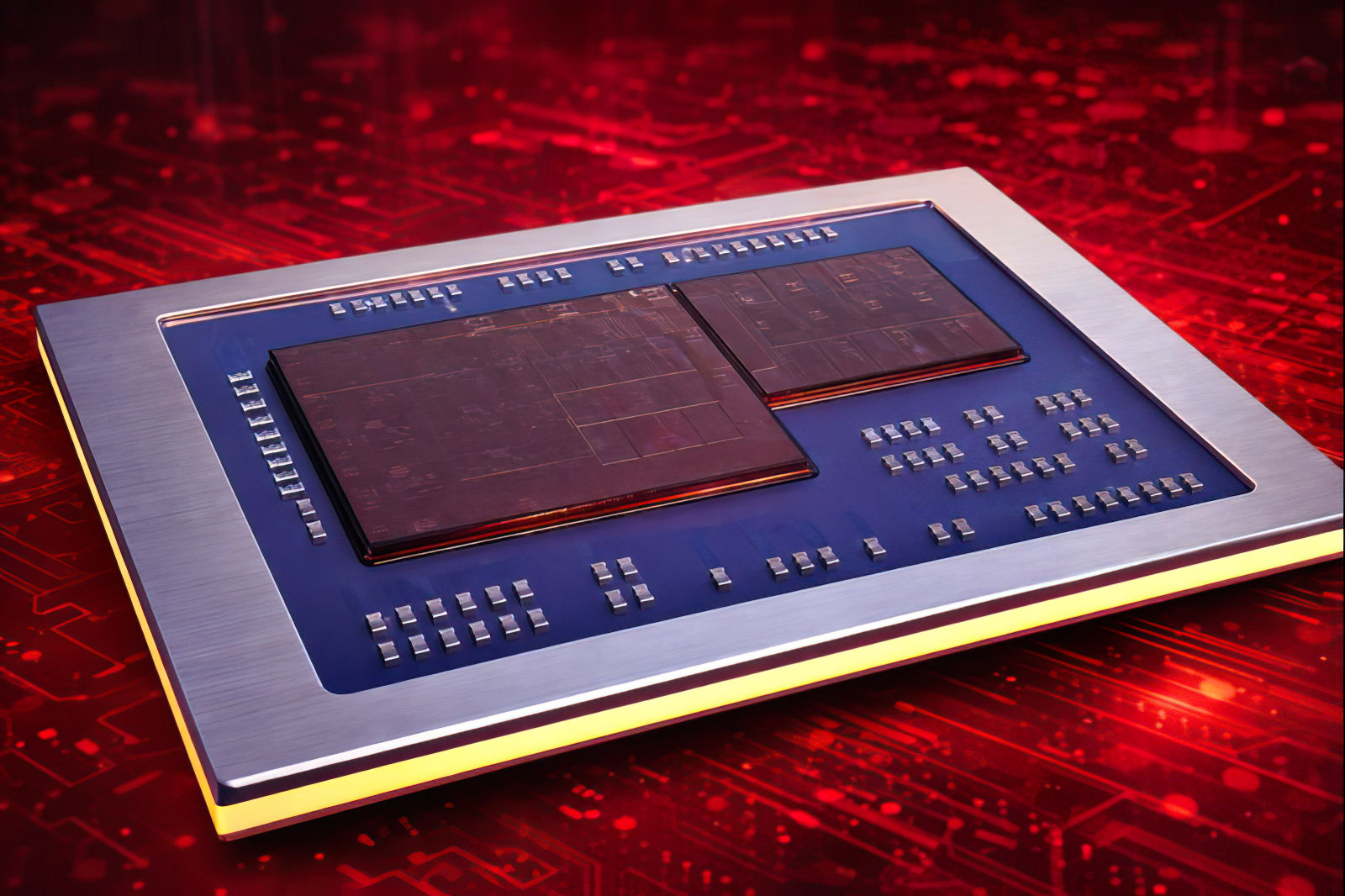

V první řadě je potvrzena jednotná L3 cache pro všech osm jader v čipletu. Dozvídáme se, že vnitřní uspořádání je realizováno tak, že všech osm jader má k L3 stejný přístup. Jinými slovy CCX se zvětšil ze čtyř jader na osm (padá tím hypotetická možnost, že by zůstaly dva CCX bloky po čtyřech jádrech a sloučena by byla jen L3 cache, ke které by každý CCX přistupoval sám za sebe). CCX je nyní osmijádrový a celý čiplet označuje AMD jako CCD (Core Complex Die).

Potvrzena je rovněž (znovu) podpora SMT2 (pro úplnost připomínám, že ta má podle aktuálních informací zůstat i pro budoucí Zen 4), které lze vypnout (jako u současné generace) a běžet v režimu 1 vlákno na 1 jádro.

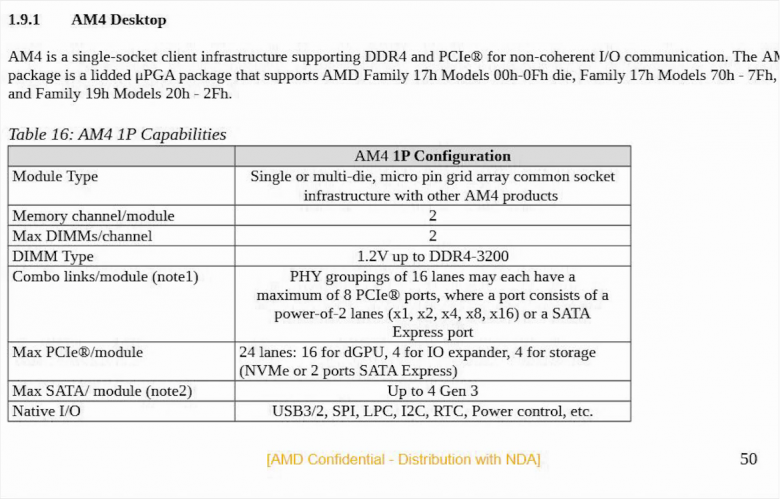

Řadič Zen 3 podporuje až 512 GB paměti na kanál, což pro dvoukanálové řešení znamená podporu až 1 TB DDR4. Podporovány jsou standardy DDR4-1333 až DDR4-3200 (více je totiž z hlediska JEDEC standardů de facto přetaktování). Centrální (IOD, NBIO) čiplet disponuje celkem 24 linkami PCIe 4.0.

Klasicky až 16 linek může využít GPU (PCIe ×16 slot), čtyři lze využít pro úložiště (NVMe, SATA Express) a čtyři podle rozhodnutí výrobce desky a využití ze strany uživatele.

K uvedení Zen 3 a desktopových procesorů Vermeer má dojít zhruba za tři týdny, ve čtvrtek 8. října. Znovu se objevila zvěst, že tato generace neponese název Ryzen 4000, ale Ryzen 5000. To by byla další indicie k náznakům, že Zen 3 APU Cezanne není daleko a pro AMD tak má smysl obě řady (Zen 3 CPU Vermeer i Zen 3 APU Cezanne) vydat v rámci totožné generace, Ryzen 5000. Ryzen 4000 tvořená Zen 2 APU Renoir by tak zůstala výhradně mobilní a OEM řadou.