Zen 5: Monolitická L2 cache pro celé CCX, L3 cache na samostatném křemíku

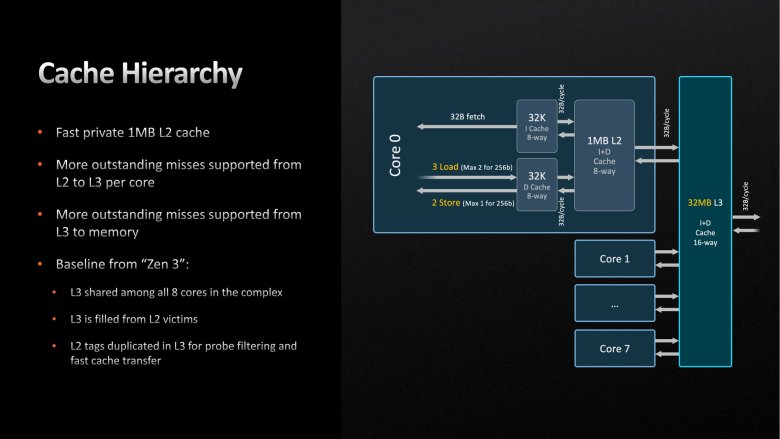

Podle dvou zdrojů webu RedGamingTech připravuje AMD se Zen 5 výrazně přepracovanou strukturu cache. V současnosti (Zen 3, Zen 4) má každé procesorové jádro vlastní L1 cache, za ní sedí L2 cache, kterou má rovněž každé jádro vlastní a teprve poté následuje L3 cache sdílená všem osmi jádrům v CCX (čipletu):

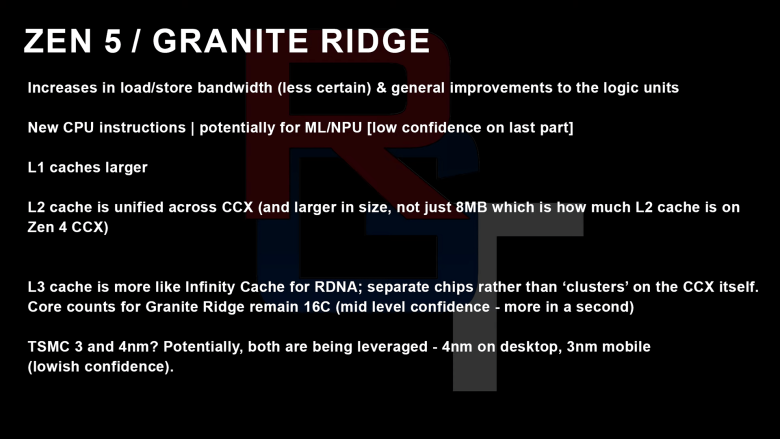

Se Zen 5 plánuje AMD sloučit L2 cache na úrovni CCX do monolitu, tedy do jedné společné sdílené. Ta navíc nemá být pouze součtem kapacit dílčích cache (u Zen 3 4 MB, u Zen 4 8 MB), ale má být větší. Že by tedy 16 MB L2 cache pro 8 jader?

Další změnou má být přesun L3 cache z CCX, tedy mimo čiplet s x86 jádry na samostatný kus křemíku. Zatím není jasné, zda to chápat tak, že vedle každého CCX (x86 čipletu) bude umístěn L3 čiplet, nebo zda bude existovat pro obě CCX jeden větší společný čiplet s L3 cache. Teoreticky by tato definice připouštěla i variantu přesunutí L3 čistě na úroveň V-cache, ale to je poněkud v rozporu s tvrzením AMD, že i Zen 5 bude mít variantu s V-cache (jinými slovy musela by existovat i varianta bez V-cache). V hypotetické rovině sice není ani to nemožné (pokud by L2 dosahovala kapacity 16 MB a k tomu byla rychlejší, z principu by nic nebránilo existenci varianty bez V-cache, tedy „jen“ s L2, ale to už se dostáváme na velmi tenký led spekulací).

AMD by spojením a sdílením L2 cache získala mimo jiné podstatně nižší latence mezi x86 jádry. Což působí jako opačná filozofie oproti Intelu, který kombinací velkých a malých jader naopak latence mezi jednotlivými x86 jádry navýšil. Je to trochu paradox - možná si ještě vzpomenete na chlubení Intelu nízkými latencemi mezi jádry u jeho 4-6jádrových procesorů oproti prvním dvěma generacím Zenu, u nichž byla i L3 rozdělena na dva samostatně fungující bloky.

Očekává se, že takty Zen 5 mezigeneračně nijak výrazně nezmění (o čemž se hovoří už delší dobu) a výkon na jádro stoupne o 20-30 %. To by vyžadovalo posun IPC nejvyšší od první generace Zenu.

RedGamingTech upozornil, že ač AMD experimentovala s vyšším počtem jader, aktuálně to vypadá, že desktopový Zen 5 zůstane na šestnácti. To může mít dva důvody. Prvním je, že desktopová verze má být postavena na 4nm procesu (derivát 5nm výroby), nikoli 3nm procesu, který by sice jádra i spotřebu zmenšil a poskytl více prostoru pro další, ale který nabral oproti původním plánům TSMC určité zpoždění a který bude ve spojitosti se Zen 5 použit nejspíš jen v mobilním segmentu.

Druhým důvodem může být fakt, že konkurenční Meteor Lake má podle některých zdrojů nést pouze 6 velkých (a 16 malých) jader, což nedává prostor pro nějaký extrémní mezigenerační nárůst výkonu oproti Raptor Lake.

| Pokud by však [u Meteor Lake] nedošlo ani na konfiguraci 8+16, ale jen 6+16, byla by ve srovnání s například 24 velkými jádry Zen 5 neuvěřitelně slabá. V takovém případě by nebylo divu, pokud by AMD se Zen 5 zůstala u maximálně 16 jader, neboť i to by na Meteor Lake 6+16 mohlo při dostatečném navýšení IPC stačit. |

Pro AMD by tak mohlo být schůdné zůstat u Zen 5 na šestnácti jádrech, která by oproti Meteor Lake mohla slušně obstát a generaci Arrow Lake, která vrátí počet velkých jader na 8 (a malých zůstane 16) konkurovat až do příchodu 3nm Zen 6 variantou Zen 5 s V-cache.

Zen 5 má dále přinést přepracovaný a rozšířený front-end, což však máme více-méně potvrzeno i přímo od AMD (úvodní slajd), L1 cache se rovněž dočká vyšší kapacity a přibude podpora nových instrukcí, nejspíš souvisejících s AI / strojovým učením.