AMD chystá revoluci v cache: SLC, jednotná L2, L3 přesunutá do V-cache

Že se v tomto směru něco děje, již nějakou dobu víme. Máme tu serverový Milan-X, jehož L3 cache je zvětšena o V-cache. V desktopu jde tento týden na trh podobně vybavený Ryzen 7 5800X3D zaměřený na hráče. V grafickém segmentu implementovala AMD Infinity Cache, která se koncem letošního roku dostane u větších GPU vně hlavní křemík do samostatných menších čipletů. Různé útržkovité zprávy ale naznačují, že ani to nebude konec a velké změny se teprve chystají.

APU - SLC (System Level Cache)

Po delší době je opět slyšet o SLC neboli o Infinity Cache unifikované pro GPU i CPU část APU. Tato myšlenka dává dobrý smysl - pokud bude v čipu implementována větší cache, je výhodné, aby ji mohla využívat procesorová i grafická jádra. Navíc existuje řada úloh, ve které je z většiny zatížená jen procesorové nebo jen grafická část - a v takových bude mít vytížená část prakticky celou cache pro sebe.

O SLC se mluví v souvislosti s APU Phoenix, což bude příští zimu uvedené spojení Zen 4 a RDNA 2. Phoenix by měl opět podstatně zvýšit grafický výkon. Stávající Rembrandt disponuje 12 CU (768 stream-procesory) a Phoenix by jich měl nabídnout podle jednoho zdroje 16+ (1024), podle jiného 16-24 (1024-1536). Zdá se tedy, že lze celkem bezpečně mluvit o ~50% navýšení výkonu. Takovému řešení by větší grafická cache prospěla, na druhou stranu by ještě nebyla bezpodmínečně nutná.

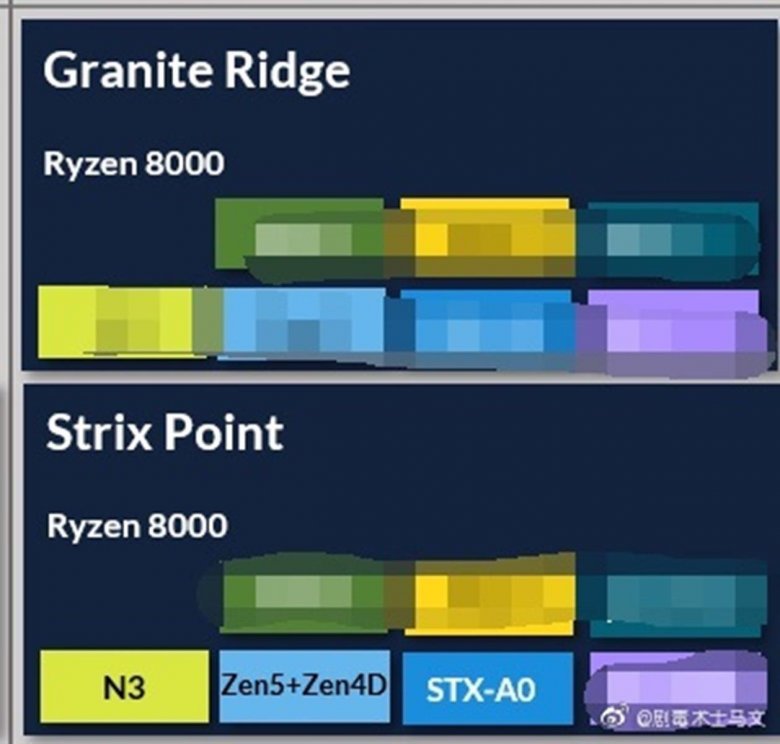

To je možná důvodem, že některé zdroje (byť minoritní) hovoří o SLC až v souvislosti s APU Strix Point (Zen 5). Může to být právě přístupem AMD, která mnohé novinky implementuje postupně a takovým způsobem, aby produkt mohl být vydán i bez nich. Viz například V-cache pro Zen 3 - procesory byly od začátku navržení tak, aby jí mohly používat, ale samy o sobě (ani jejich vydání) na V-cache nebylo závislé. Podobně to může být s SLC, která se může ukázat s generací Phoenix, ale v případě zdržení jejího vývoje může být vydán i bez ní. Zatím nevíme, zda by tato SLC byla implementována na úrovni jádra nebo volitelně formou V-cache.

V-cache namísto L3 u velkých procesorů

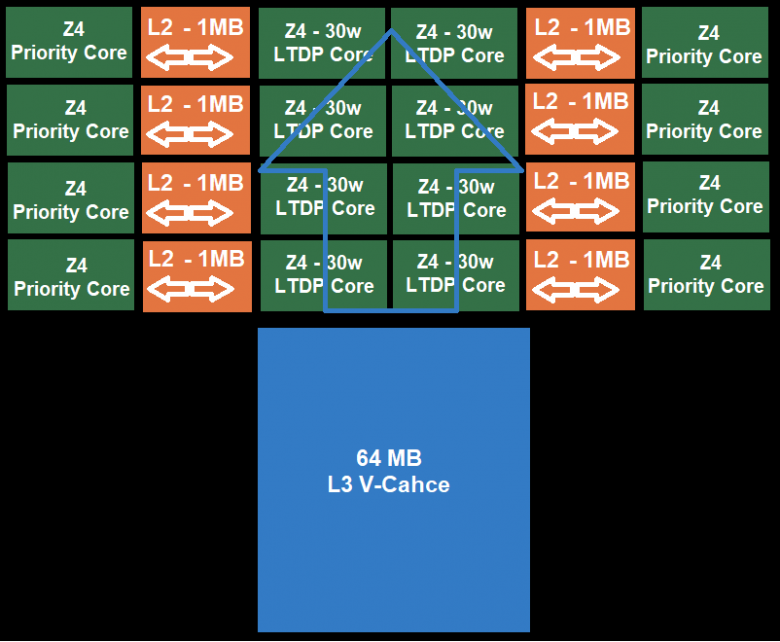

Současný koncept, kdy jsou procesorové čiplety vybaveny L3 cache a další lze implementovat prostřednictvím V-cache, není podle všeho pro AMD cílem, ale technologickým přechodem. Ten umožňuje, jak již bylo řečeno, vydat funkční produkt nezávisle na tom, zda je nová technologie doladěna, a zároveň novou technologii implementovat do praxe a s její pomocí vytvořit nový produkt. Zen 3 s V-cache se jeví jako první krok tohoto procesu. Další je zachycen na schematu, které od loňska koluje internetem, které zachycuje jádra Zen 4 bez L3 cache, která jsou překrytá L3 cache v podobě V-cache.

Vzhledem k tomu, že takový koncept nemá být použit na žádném klíčovém Zen 4 produktu (ani Raphael pro AM5 desktop, ani APU Phoenix, ani Epyc Genoa pro servery), zbývá vylučovací metodou pouze Epyc Bergamo (128jádrové řešení orientované na poměr spotřeba / výkon). Tento produkt, který opět není nezbytný pro kompletaci produktového portfolia, by teoreticky mohl posloužit jako testovací platforma pro implementaci myšlenky kompletního přesunutí L3 cache na úroveň V-cache.

Třetí - klíčový - krok pak přijde s generací Zen 5. Nejen, že by Zen 5 měl mít standardně přesunutou L3 cache na úroveň V-cache (což umožňuje ušetřit podstatnou plochu jádra, respektive tuto plochu věnovat samotnému x86 jádru pro zvýšení IPC a zároveň tím vyřešit bolest nových výrobních procesů, které čím dál méně zmenšují SRAM), ale zároveň dojde i na přepracování L2 cache. Ta je v současnosti 0,5MB (pro Zen 3) nebo 1MB (pro Zen 4) na každé procesorové jádro. Každé jádro má tedy vlastní malou L2 cache - nezávislou na zbytku. Zen 5 přinese unifikovanou L2 cache, kdy osm jader bude vybaveno jednou velkou 8MB L2 cache. Výhoda je podobná, jako když se Zen 3 AMD spojila dvě oddělené L3 cache v jednu dvojnásobnou. V situacích, kdy má každé jádro jiný požadavek na kapacitu cache, nemusí být výkon jednotlivých jader limitován kapacitou 1MB L2 cache, ale může využít i více. Při zátěži nižšího počtu jader jsou pak jednotlivým jádrům k dispozici až násobky původní kapacity. L2 cache Zen 5 v tomto ohledu bude podobná jako L3 cache Zen 3/4.

Tato změna by mohla být jedním z řady prvků, které povedou k mezigeneračnímu nárůstu IPC Zen 5. Ten byl donedávna uváděn kolem 25 % nad Zen 4, ale poslední informace naznačují, že by mohlo být dosaženo i hodnoty kolem 30 % nad Zen 4. To je ještě hodnota, která není úplnou fantasmagorií a lze jí považovat za reálně dosažitelnou metu.

Pokud se totiž ohlédneme, můžeme si všimnout, že se AMD zatím daří navyšovat IPC s každou další generací o 5 % více než s předchozí - což evidentně působí jako vytyčený cíl. Musíme vzít v potaz, že 15% posun u Zen 2 nebyl původně plánovaný, neboť po architektonické stránce měl být Zen tím, čím se stal až Zen 2 (AMD tehdy neměla prostředky a pracovní síly k dosažení původního cíle, takže se rozhodla Zen zjednodušit a původní plán nechat pro Zen 2). Všimněte si ale nárůstů IPC:

- Zen 2: +15 %

- Zen 3: +19 %

- Zen 4: +~25%

- Zen 5: +~30%(?)

Posuny IPC samozřejmě nelze navyšovat donekončena, ale vypadá to, že zvýšení mezigeneračního nárůstu o dalších 5 % (procentních bodů) není u Zen 5 vyloučeno.

Poněkud nejednoznačné informace se zatím týkají kombinace jader Zen 5 a Zen 4. Některé zdroje předpokládají, že se kombinace architektur bude týkat pouze segmentu APU (zbytek by byl postaven čistě na jádrech Zen 5), jiné předpokládají, že se kombinace bude týkat i klasického desktopu. Nutno uznat, že první možnost (kombinace pouze u APU) by opět lépe zapadala do strategie implementace novinek takovým způsobem, aby v případě problému byly co nejméně postiženy klíčové produkty (připomeňme, že kdyby byl s APU Strix Point problém a nemohlo by být včas vydáno, nebyl by to zásadní zádrhel, neboť v té době budou již polovinu mobilního segmentu pokrývat velké procesory s malou integrovanou grafikou).

Závěrem si můžeme udělat hrubý ilustrační přehled toho, kdy se produktů s nově koncipovanými cache dočkáme:

- Q2 2022 - Ryzen 7 5800X3D (V-cache v desktopu)

- Q4 2022 - RDNA 3 (čipletová Infinity Cache u větších GPU)

- Q1 2023 - (první APU se SLC?)

- H1 2023 - Epyc Bergamo (teoretická možnost přesunu L3 do V-cache)

- Q4 2023 - Zen 5 (unifikovaná L2 cache, přesun L3 do V-cache)